TMS320C6713B

Цифровые процессоры для обработки сигналов с плавающей точкой

Отличительные особенности:

- ЦПОС с самой высокой производительностью: TMS320C6713B

- Восемь 32-разрядных инструкций/цикл

- 32/64-разрядное слово данных

- Тактовые частоты 300-, 225-, 200-МГц (GDP и ZDP), а также 225-, 200-, 167-МГц (PYP)

- Длительность цикла инструкции 3.3, 4.4, 5, 6 нс

- 2400/1800, 1800/1350, 1600/1200 и 1336/1000 миллионов инстр. в сек./миллионов операций с плавающей точкой в секунду

- Обширный набор периферийных устройств, которые оптимизированны под аудиоприложения

- Высокооптимизированный компилятор C/C++

- Доступность версии для расширенного температурного диапазона

- Ядро ЦПУ TMS320C67x с архитектурой VelociTI усовершенствованного очень длинного слова инструкции (VLIW)

- Восемь независимых функциональных блоков:

- Два АЛУ (фиксированная точка)

- Четыре АЛУ (плавающая и фиксированная точка)

- Два умножающих устройства (плавающая и фиксированная точка)

- Архитектура чтения-записи с 32 32-разрядными регистрами общего назначения

- Упаковка инструкции снижает размер кода

- Все инструкции условия

- Особенности набора инструкций

- Наследование IEEE 754-инструкций одиночной и двойной точности

- Байт-адресуемые (8-, 16-, 32-разр. данные)

- 8-разрядная защита от переполнения

- Насыщение; извлечение битового поля, установка, сброс; счет бит; нормализация

- Архитектура памяти L1/L2

- Кэш-память программ L1P размером 4 кбайт (табличный доступ)

- Кэш-память данных L1D размером 4 кбайт (2-путевой ассоциативный доступ)

- Общий размер памяти L2 256 кбайт: 64 кбайт унифицированного ОЗУ/кэш-памяти L2 и 192 кбайт дополнительного табличного ОЗУ L2

- Конфигурация устройства

- Загрузочный режим: HPI, 8-, 16-, 32-разр. загрузочное ПЗУ

- Прямой (Little Endian) и обратный (Big Endian) порядок следования байт

- 32-разрядный интерфейс внешней памяти (EMIF)

- Непосредственное подключение к асинхронной памяти: стат. ОЗУ и ЭСППЗУ

- Непосредственное подключение к синхронной памяти: SDRAM и SBSRAM

- 512 Мбайт общего адресуемого пространства внешней памяти

- Контроллер расширенного прямого доступа к памяти (EDMA) (16 раздельных каналов)

- 16-разрядный интерфейс хост-порта (HPI)

- Два McASP

- Две раздельных зоны синхронизации в каждом блоке (1 зона передачи и 1 зона приема)

- Восемь выводов последовательных данных на каждый порт: раздельное назначение на работу с любой зоной синхронизации

- Каждая зона синхронизации содержит:

- Программируемый тактовый генератор

- Программируемый генератор синхронизации кадра

- TDM-потоки с 2-32 временными интервалами

- Поддержка размеров посылки: 8, 12, 16, 20, 24, 28, 32 бит

- Форматировщик данных для манипуляции над битом

- Поддержка форматов битового потока I2S и подобных ему

- Встроенный передатчик цифрового аудиоинтерфейса (DIT) поддерживает:

- Форматы S/PDIF, IEC60958-1, AES-3, CP-430

- До 16 выводов передачи

- Расширенный статус канала/данные пользователя

- Исчерпывающий контроль и исправление ошибок

- Два шинных интерфейса I2C с поддержкой многомастерной и подчиненного режимов

- Два многоканальных буферизованных последовательных порта:

- Последовательный интерфейс SPI

- Высокоскоростной интерфейс TDM

- Интерфейс AC97

- Два 32-разрядных таймера общего назначения

- Выделенный модуль ввода-вывода с 16 выводами (возможность работы в качестве входов внешних прерываний)

- Модуль тактового генератора на основе конфигурируемой схемы ФАПЧ

- Граничное сканирование в соответствии с IEEE-1149.1 (JTAG)

- 208-выв. корпус PowerPAD PQFP (PYP)

- 272-выв. корпус BGA (GDP и ZDP)

- Технология 0.13 мкм с 6-уровневой медной металлизацией

- 3.3В-ый ввод-вывод, внутреннее питание 1.2В (GDP/ZDP/ PYP)

- 3.3В-ый ввод-вывод, внутреннее питание 1.4В (GDP/ZDP) [300 МГц]

Структурная схема:

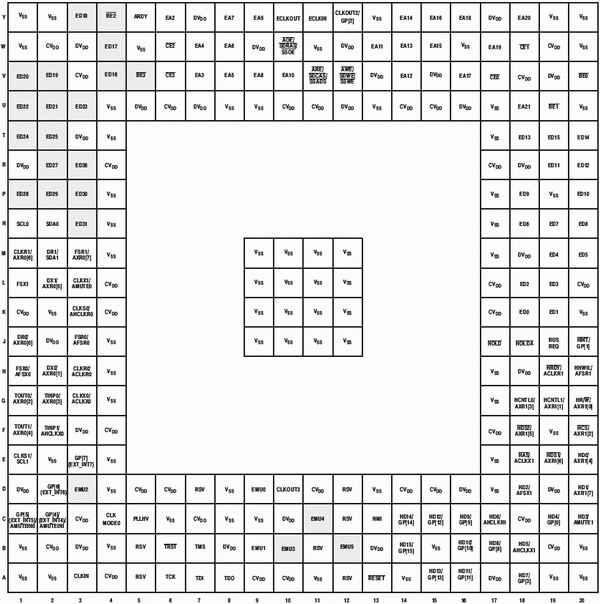

Расположение выводов в 208-выводном корпусе PowerPAD PQFP:

Расположение выводов в 272-выводных корпусах BGA GDP и ZDP (вид снизу):

Общее описание:

ЦПОС TMS320C67x (в т.ч. TMS320C6713B) представляют семейство ЦПОС с плавающей запятой в составе платформы TMS320C6000. C6713B выполнен на основе высокопроизводительной, усовершенствованной архитектуры VelociTI очень длинного слова инструкции (VLIW), которая разработана Texas Instruments и делает данные ЦПОС превосходным выбором для применения в многоканальных и многофункциональных приложениях.

На тактовой частоте 225 МГц C6713B достигает производительности 1,35 млрд. операций с плавающей точкой в секунду и 1,8 млрд. инструкций в секунду, а с помощью двух умножающих устройств позволяет выполнить 450 млн. умножений-накоплений в секунду.

На тактовой частоте 300 МГц C6713B достигает производительности 1,8 млрд. операций с плавающей точкой в секунду и 2,4 млрд. инструкций в секунду, а с помощью двух умножающих устройств позволяет выполнить 600 млн. умножений-накоплений в секунду.

C6713B использует двухуровневую архитектуру кэш-памяти и интегрирует мощный и разнообразный набор периферийных устройств. Кэш-память программ 1 уровня (L1P) имеет размер 4 кбайт и табличную организацию, а кэш-память данных данных 1 уровня (L1D) имеет размер 4 кбайт и двухпутевой ассоциативный доступ. Кэш-память 2 уровня (L2) состоит из пространства памяти размером 256 кбайт, которое совместно используется пространствами памяти программ и данных. 64 кбайт из 256 кбайт памяти L2 может конфигурироваться как табличная память, кэш-память или как сочетание двух. Оставшиеся 192 кбайт в памяти L2 функционируют как табличное статическое ОЗУ.

В состав периферийных устройств C6713B входят: два многоканальных последовательных аудиопорта (McASP), два многоканальных буферизованных последовательных порта (McBSP), два шинных интерфейса I2C, один выделенный модуль ввода-вывода общего назначения, два таймера общего назначения, интерфейс хост-порта (HPI) и и интерфейс внешней памяти (EMIF) для непосредственного подключения SDRAM, SBSRAM и асинхронной памяти.

Два интерфейсных модуля McASP с поддержкой одной зоны синхронизации передачи и одной зоны синхронизации приема каждым. Каждый из модулей McASP содержит 8 выводов последовательных данных, которые раздельно могут быть настроены на работу с любой из зон. Последовательный порт поддерживает мультиплексирование с разделением по времени на каждом выводе с 2..32 временными интервалами. C6713B характеризуется достаточным быстродействием для одновременной передачи на всех 16 выводах последовательных данных стереосигнала 192 кГц. Последовательные данные в каждой зоне могут передаваться и приниматься по нескольким выводам последовательных данных одновременно с использованием различных вариаций форматов Philips I2S.

Кроме того, передатчик McASP может программироваться на вывод нескольких кодированных каналов данных S/PDIF, IEC60958, AES-3, CP-430 с хранением в одном ОЗУ всех данных пользователя и полей статуса каналов.

McASP также выполняет функции выявления и исправления ошибок, как, например, схема детекции нарушения синхронизации, которая проверяет нахождение в допустимых границах частоты сигнала ведущей синхронизации.

Два порта I2C в составе TMS320C6713B позволяют ЦПОС легко управлять периферийными устройствами и связаться с хост-процессором. Кроме того, стандартный многоканальный буферизованный последовательный порт (McBSP) может использоваться для связи с устройствами, содержащие последовательный интерфейс SPI.

TMS320C6713B поддерживает два загрузочных режима: через HPI или из внешнего асинхронного ПЗУ.

Поколение ЦПОС TMS320C67x поддерживается набором средств для проектирования eXpressDSP, в т.ч.высокооптимизированный компилятор C/C++, интегрированная среда для проектирования "Code Composer Studio", эмуляторы и реально-временные отладчики на основе стандарта JTAG и ядро ЦПОС/BIOS (базовая система ввода-вывода).

Документация:

| |

|

2189 kB Engl Полное описание микросхем |

|