21. Интерфейс программирования флэш-памяти (FFPI)

21.1 Обзор

Интерфейс программирования флэш-памяти сориентирован для серийного производства. Программирование осуществляется по параллельному или последовательному интерфейсу. Для программирования используются стандартные промышленные программаторы. Параллельный интерфейс очень удобен, так как в этом случае устройство определяется как стандартная память EEPROM. Вдобавок, при параллельном программировании возможен доступ ко всем встроенным возможностям флэш-памяти.

Режим программирования флэш-памяти не предназначен для внутрисхемного программирования.

21.2 Параллельный режим программирования флэш-памяти

21.2.1 Конфигурация устройства

В режиме программирования флэш-памяти микроконтроллер находится в особом тестовом режиме. В этом режиме используется часть выводов, остальные выводы должны быть отключены.

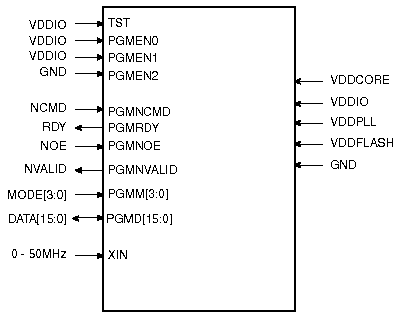

Рис. 21-1. Включение AT91SAM7S256/128/64/321 при параллельном интерфейсе программирования

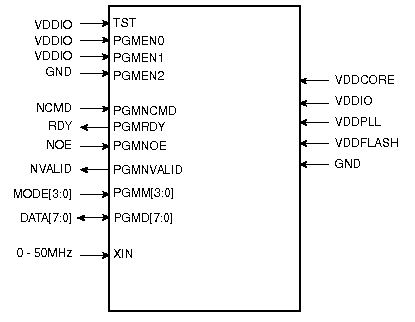

Рис. 21-2. Включение AT91SAM7S32 при параллельном интерфейсе программирования

Таблица 21-1 Описание выводов

| Сигнал |

Назначение |

Тип |

Активный уровень |

Примечания |

| Питание |

| VDDFLASH |

Питание флэш-памяти |

Питание |

|

|

| VDDIO |

Питание буферов портов ввода/вывода |

Питание |

|

|

| VDDCORE |

Питание ядра |

Питание |

|

|

| VDDPLL |

Питание PLL (ФАПЧ) |

Питание |

|

|

| GND |

Земля |

Земля |

|

|

| Тактовые сигналы |

| XIN |

Вход основного тактового генератора. Может быть подключен к цепи GND, в этом случае микроконтроллер тактируется от внутреннего RC генератора. |

Вход |

|

От 32кГц до 50МГц |

| Сигналы выбора тестового режимов |

| TST |

Выбор тестового режима |

Вход |

Высокий |

Подтянут к VDDIO |

| PGMENO |

Выбор тестового режима |

Вход |

Высокий |

Подтянут к VDDIO |

| PGMEN1 |

Выбор тестового режима |

Вход |

Высокий |

Подтянут к VDDIO |

| PGMEN2 |

Выбор тестового режима |

Вход |

Низкий |

Подтянут к GND |

| Сигналы программирования |

| PGMNCMD |

Команда программирования |

Вход |

Низкий |

Подтянут к VDDIO после сброса |

| PGMRDY |

0: устройство занято

1: устройство готово для новой команды |

Выход |

Высокий |

Подтянут к VDDIO после сброса |

| PGMNOE |

Разрешение выходов (active high) |

Вход |

Низкий |

Подтянут к VDDIO после сброса |

| PGMNVALID |

Направление передачи данных

0: DATA[15:0] или DATA[8:0](1) в режиме ввода

1: DATA[15:0] или DATA[8:0](1) в режиме вывода |

Выход |

Низкий |

Подтянут к VDDIO после сброса |

| PGMM[3:0] |

Режим программирования (см. Таблицу 21-2) |

Вход |

|

Подтянуты к VDDIO после сброса |

| PGMD[15:0] или [8:0](2) |

Двунаправленная шина данных |

Вход/ Выход |

|

Подтянуты к VDDIO после сброса |

Примечания:

- DATA[8:0] для AT91SAM7S32.

- PGMD[8:0] для AT91SAM7S32.

21.2.2 Описание сигналов

Данные c шины DATA загружаются в различные внутренние регистры в зависимости от установок сигналов MODE.

Таблица 21-2 Установка режимов сигналами MODE

| MODE[3:0] |

Режим |

Запись данных в регистр |

| 0000 |

CMDE |

Запись в Регистр команд |

| 0001 |

ADDR0 |

Запись в Регистр адреса - младший байт |

| 0010 |

ADDR1 |

|

| 0011 |

ADDR2 |

|

| 0100 |

ADDR2 |

Запись в Регистр адреса - старший байт |

| 0101 |

DATA |

Запись в Регистр данных |

| Остальные значения |

IDLE |

- |

Примечание: DATA[8:0] для AT91SAM7S32.

Таблица 21-3. Коды команд для работы с флэш-памятью

| DATA[15:0] или DATA[8:0](1) |

Обозначение команды |

Выполнение команды |

| 0x0011 |

READ |

Чтение Флэш-памяти |

| 0x0012 |

WP |

Запись страницы флэш-памяти |

| 0x0022 |

WPL |

Запись страницы и установка защиты |

| 0x0032 |

EWP |

Стирание и запись страницы |

| 0x0042 |

EWPL |

Стирание и запись страницы, затем установка защиты |

| 0x0013 |

EA |

Стереть все |

| 0x0014 |

SLB |

Установить защиту |

| 0x0024 |

CLB |

Снять защиту |

| 0x0015 |

GLB |

Чтение бит защиты |

| 0x0034 |

SFB |

Установить NVM бит |

| 0x0044 |

CFB |

Сбросить NVM бит |

| 0x0025 |

GFB |

Чтение NVM бит |

| 0x0054 |

SSE |

Установить бит секретности |

| 0x0035 |

GSE |

Чтение бита секретности |

| 0x001E |

GVE |

Проверка версии |

Примечание: DATA[8:0] для AT91SAM7S32

21.2.3 Режим программирования

Для входа в режим программирования флэш-памяти необходимо выполнить:

- Подключить цепи GND, VDDIO, VDDCORE, VDDFLASH, VDDPLL;

- Подключить тактовый вход XIN в течение интервала TPOR_RESET при использовании внешнего тактового генератора;

- Выждать интервал TPOR_RESET;

- Начать операцию чтения/записи.

Примечание: после сброса микроконтроллер тактируется от внутреннего RC генератора. Перед сбросом сигнала RDY, если внешний тактовый генератор (> 32 кГц) подключен к входу XIN, микроконтроллер переключится на внешний генератор, в противном случае вход XIN не подключается. Более высокая частота на входе XIN повышает скорость обмена данными с программатором.

21.2.3.1 Циклы программирования

Циклы программирования определены для операций чтения и записи. Когда микроконтроллер готов к выполнению новой команды (установлен сигнал RDY), программатор начинает рабочий цикл сбросом сигнала NCMD. Цикл завершается, когда оба сигнала NCMD и RDY имеют высокий уровень.

21.2.3.2 Цикл записи.

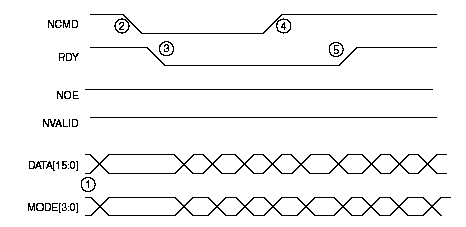

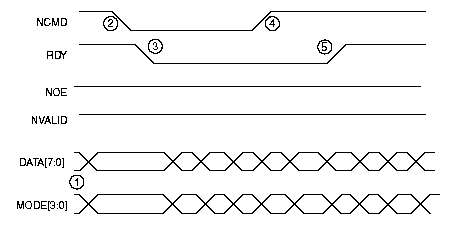

Работа цикла записи поясняется рис.21-3, рис.21-4 и таблицей 21-4.

Рис.21-3 Цикл записи при параллельном программировании AT91SAM256/128/64/321

Рис.21-4 Цикл записи при параллельном программировании AT91SAM7S32

Таблица 21-4 Цикл записи

| Шаг |

Действия программатора |

Действия микроконтроллера |

Данные |

| 1 |

Установка сигналов MODE и DATA |

Ожидание низкого уровня NCMD |

Вход |

| 2 |

Сброс сигнала NCMD |

Фиксация сигналов MODE и DATA |

Вход |

| 3 |

Ожидание низкого уровня RDY |

Сброс сигнала RDY |

Вход |

| 4 |

Отключение сигналов MODE и DATA |

Выполнение команды и установка сигнала NCMD |

Вход |

| 5 |

Установка сигнала NCMD |

Выполнение команды и установка сигнала NCMD |

Вход |

| 6 |

Ожидание высокого уровня RDY |

Установка RDY |

Вход |

21.2.3.3 Цикл чтения

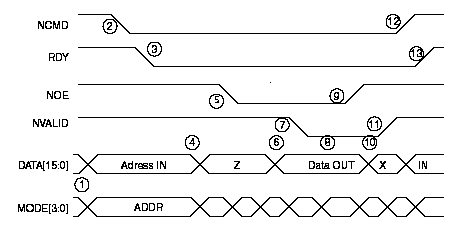

Работа цикла чтения поясняется рис.21-5, рис.21-6 и таблицей 21-5

Рис.21-5 Цикл чтения при параллельном программировании AT91SAM256/128/64/321

Рис.21-6 Цикл чтения при параллельном программировании AT91SAM7S32

Таблица 21-5 Цикл чтения

| Шаг |

Действия программатора |

Действия микроконтроллера |

Данные |

| 1 |

Установка сигналов MODE и DATA |

Ожидание низкого уровня NCMD |

Вход |

| 2 |

Сброс сигнала NCMD |

Фиксация сигналов MODE и DATA |

Вход |

| 3 |

Ожидание низкого уровня RDY |

Сброс сигнала RDY |

Вход |

| 4 |

Установка сигналов DATA в высоко импедансное состояние (Tristate) |

Ожидание низкого уровня NOE |

Вход |

| 5 |

Сброс сигнала NOE |

|

Tristate |

| 6 |

Ожидание низкого уровня NVALID |

Установка шины DATA в режим вывода и вывод содержимого flash памяти |

Выход |

| 7 |

|

Сброс сигнала NVALID |

Выход |

| 8 |

Чтение данных с шины DATA |

Ожидание высокого уровня NOE |

Выход |

| 9 |

Установка сигнала NOE |

|

Выход |

| 10 |

Ожидание высокого уровня NVALID |

Установка шины DATA в режим ввода |

X |

| 11 |

Установка шины DATA в режим вывода |

Установка сигнала NVALID |

Вход |

| 12 |

Установка сигнала NCMD |

Ожидание высокого уровня NCMD |

Вход |

| 13 |

Ожидание высокого уровня RDY |

Установка сигнала RDY |

Вход |

21.2.4 Работа микроконтроллера с флэш-памятью

Команды для работы с флэш-памятью сведены в таблицу 21-3. Каждая команда выполняется программатором через параллельный интерфейс в нескольких последовательных циклах чтения/записи.

Выполнение команды чтения непосредственно после команды записи автоматически очищает буфер записи

.

В таблицах с 21-6 по 21-14

- DATA[15:0] для AT91SAM7S256/128/64/321

- DATA[8:0] для AT91SAM7S32

21.2.4.1 Команда чтения флэш-памяти

Операция чтения осуществляется с любого адреса в пространстве флэш-памяти и оптимизирована для последовательного чтения (без повторного указания полного адреса). В этом случае внутренний адресный буфер автоматически инкрементируется.

Таблица 21-6 Выполнение команды чтения

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

READ |

| 2 |

Цикл записи |

ADDRO |

32-битный адрес флэш-памяти (первый байт) |

| 3 |

Цикл записи |

ADDR1 |

32-битный адрес флэш-памяти (второй байт) |

| 4 |

Цикл записи |

ADDR2 |

32-битный адрес флэш-памяти (третий байт) |

| 5 |

Цикл записи |

ADDR3 |

32-битный адрес флэш-памяти (последний байт) |

| 6 |

Цикл чтения |

DATA |

*Инкрементирование адреса памяти |

| 7 |

Цикл чтения |

DATA |

* Инкрементирование адреса памяти |

| … |

… |

… |

… |

| n |

Цикл записи |

ADDRO |

32-битный адрес флэш-памяти (первый байт) |

| n+1 |

Цикл записи |

ADDR1 |

32-битный адрес флэш-памяти (второй байт) |

| n+2 |

Цикл записи |

ADDR2 |

32-битный адрес флэш-памяти (третий байт) |

| n+3 |

Цикл записи |

ADDR3 |

32-битный адрес флэш-памяти (последний байт) |

| n+4 |

Цикл чтения |

DATA |

*Инкрементирование адреса памяти |

| n+5 |

Цикл чтения |

DATA |

*Инкрементирование адреса памяти |

| … |

… |

… |

… |

21.2.4.2 Команда записи флэш-памяти

Пространство флэш-памяти разбито на страницы. Записываемые данные хранятся в буфере записи, размер которого соответствует одной странице памяти. Содержимое буфера записи автоматически переносится во флэш-память:

- при обращении к любой странице отличной от текущей,

- поступает новая команда (MODE = CMDE).

Команда "Write Page" ("Запись страницы") WP оптимизирована для последовательной записи (без повторного указания полного адреса). В этом случае внутренний адресный буфер автоматически инкрементируется.

Таблица 21-7 Выполнение команд записи

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

Команды WP,WPL,EWP или EWPL |

| 2 |

Цикл записи |

ADDRO |

32-битный адрес флэш-памяти (первый байт) |

| 3 |

Цикл записи |

ADDR1 |

32-битный адрес флэш-памяти (второй байт) |

| 4 |

Цикл записи |

ADDR2 |

32-битный адрес флэш-памяти (третий байт) |

| 5 |

Цикл записи |

ADDR3 |

32-битный адрес флэш-памяти (последний байт) |

| 6 |

Цикл записи |

DATA |

*Инкрементирование адреса памяти |

| 7 |

Цикл записи |

DATA |

* Инкрементирование адреса памяти |

| … |

… |

… |

… |

| n |

Цикл записи |

ADDRO |

32-битный адрес флэш-памяти (первый байт) |

| n+1 |

Цикл записи |

ADDR1 |

32-битный адрес флэш-памяти (второй байт) |

| n+2 |

Цикл записи |

ADDR2 |

32-битный адрес флэш-памяти (третий байт) |

| n+3 |

Цикл записи |

ADDR3 |

32-битный адрес флэш-памяти (последний байт) |

| n+4 |

Цикл записи |

DATA |

*Инкрементирование адреса памяти |

| n+5 |

Цикл записи |

DATA |

*Инкрементирование адреса памяти |

| … |

… |

… |

… |

Команда Запись страницы и защита (Write Page and Lock) WPL аналогична команде записи, но при этом в конце операции записи автоматически устанавливается бит защиты (lock бит). Так как область защиты включает несколько страниц, программатор записывает первые страницы блокируемой области, используя команду WP, а последнюю страницу записывает командой WPL.

Команда Стирание страницы и запись (Erase Page and Write) EWP. Перед заполнением буфера записи страница стирается.

Команда Стирание страницы запись и защита (Erase Page and Write the Lock) является комбинацией команд EWP и WPL.

21.2.4.3 Команда полного стирания флэш-памяти.

Перед полным стиранием флэш-памяти со всех защищенных областей флэш-памяти должна быть снята защита командой CLB. В противном случае операция стирания не будет выполнена.

Таблица 21-8. Команда полного стирания флэш-памяти

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

EA |

| 2 |

Цикл записи |

DATA |

0 |

21.2.4.4 Команды защиты флэш-памяти

Биты защиты устанавливаются командами WPL или EWPL. Командой установки защиты (Set Lock Bit) SLB могут быть активированы несколько бит защиты. В этом случае совместно с командами SLB/CLB используется дополнительный аргумент Маска защиты (Bit Mask). Установка нулевого бита маски защиты активирует соответственно первый бит защиты.

Для сброса битов защиты используется команда Снять защиту (Clear Lock Bit) CLB. Все биты защиты сбрасываются также командой EA.

Таблица 21-9 Команды установки/сброса бит защиты

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

SLB или CLB |

| 2 |

Цикл записи |

DATA |

Маска защиты |

Чтение битов защиты осуществляется командой Get Lock Bit (GLB). В маске защиты установленному n-ому биту соответствует активный n-ый бит защиты.

Таблица 21-10 Команда чтения битов защиты GLB

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

GLB |

| 2 |

Цикл чтения |

DATA |

Статус бита в маске защиты

0 = Бит защиты сброшен

1 = Бит защиты установлен |

21.2.4.5 Команды управления NVM битами защиты

Общие NVM биты защиты (GP NVM биты) устанавливаются командой Set Fuse Bit (SFB). При этом соответствующие биты активируются. С командой также используется аргумент Маска защиты (Bit Mask).

Установка нулевого бита маски защиты активирует соответственно первый бит защиты GP NVM.

Команда Clear Fuse Bit (CFB) используется для сброса GP NVM бит. GP NVM биты также сбрасываются командой EA. GP NVM биты деактивируются, когда соответствующие биты в Маске GP NVM установлены в 1.

Таблица 21-11 Команда установки/сброса GP NVM бит

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

SFB или CFB |

| 2 |

Цикл записи |

DATA |

Маска GP NVM бит |

GP NVM биты читаются командой Get Fuse Bit (GFB). В маске GP NVM установленному n-ому биту соответствует активный n-ый GP NVM бит.

Таблица 21-12 Команда чтения GP NVM бит

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

GFB |

| 2 |

Цикл чтения |

DATA |

Статус бита в маске GP NVM

0 = GPNVM бит сброшен

1 =GPNVM бит установлен |

21.2.4.6 Бит секретности флэш-памяти

Бит секретности устанавливается командой Set Security Bit (SSE). При активном бите секретности программирование флэш-памяти невозможно. Сброс бита защиты возможен только с полным стиранием содержимого флэш-памяти.

Таблица 21-13 Команда установки бита секретности

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

SSE |

| 2 |

Цикл записи |

DATA |

0 |

21.2.4.7 Команда чтения памяти

Операция чтения (RRAM) осуществляется с любого адреса в пространстве памяти и оптимизирована для последовательного чтения (без повторного указания полного адреса). В этом случае внутренний адресный буфер автоматически инкрементируется.

Таблица 21-14 Команда чтения

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

RRAM |

| 2 |

Цикл записи |

ADDRO |

32-битный адрес флэш-памяти (первый байт) |

| 3 |

Цикл записи |

ADDR1 |

32-битный адрес флэш-памяти (второй байт) |

| 4 |

Цикл записи |

ADDR2 |

32-битный адрес флэш-памяти (третий байт) |

| 5 |

Цикл записи |

ADDR3 |

32-битный адрес флэш-памяти (последний байт) |

| 6 |

Цикл чтения |

DATA |

*Установка адреса памяти на 1 больше |

| 7 |

Цикл чтения |

DATA |

*Установка адреса памяти на 1 больше |

| … |

… |

… |

… |

| n |

Цикл записи |

ADDRO |

32-битный адрес флэш-памяти (первый байт) |

| n+1 |

Цикл записи |

ADDR1 |

32-битный адрес флэш-памяти (второй байт) |

| n+2 |

Цикл записи |

ADDR2 |

32-битный адрес флэш-памяти (третий байт) |

| n+3 |

Цикл записи |

ADDR3 |

32-битный адрес флэш-памяти (последний байт) |

| n+4 |

Цикл чтения |

DATA |

*Установка адреса памяти на 1 больше |

| n+5 |

Цикл чтения |

DATA |

*Установка адреса памяти на 1 больше |

| … |

… |

… |

… |

21.2.4.8 Команда записи в память

Команда записи (WRAM) осуществляется с любого адреса в пространстве памяти и оптимизирована для последовательной записи (без повторного указания полного адреса). В этом случае внутренний адресный буфер автоматически инкрементируется.

Таблица 21-15 Команда записи

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

WRAM |

| 2 |

Цикл записи |

ADDRO |

32-битный адрес флэш-памяти (первый байт) |

| 3 |

Цикл записи |

ADDR1 |

32-битный адрес флэш-памяти (второй байт) |

| 4 |

Цикл записи |

ADDR2 |

32-битный адрес флэш-памяти (третий байт) |

| 5 |

Цикл записи |

ADDR3 |

32-битный адрес флэш-памяти (последний байт) |

| 6 |

Цикл записи |

DATA |

*Установка адреса памяти на 1 больше |

| 7 |

Цикл записи |

DATA |

*Установка адреса памяти на 1 больше предыдущего |

| … |

… |

… |

… |

| n |

Цикл записи |

ADDRO |

32-битный адрес флэш-памяти (первый байт) |

| n+1 |

Цикл записи |

ADDR1 |

32-битный адрес флэш-памяти (второй байт) |

| n+2 |

Цикл записи |

ADDR2 |

32-битный адрес флэш-памяти (третий байт) |

| n+3 |

Цикл записи |

ADDR3 |

32-битный адрес флэш-памяти (последний байт) |

| n+4 |

Цикл записи |

DATA |

*Установка адреса памяти на 1 больше |

| n+5 |

Цикл записи |

DATA |

*Установка адреса памяти на 1 больше предыдущего |

| … |

… |

… |

… |

21.2.4.9 Команда чтения версии

Команда чтения версии Get Version (GVE) выдает информацию по версии FFPI интерфейса.

Таблица 21-16 Команда проверки версии

| Шаг |

Последовательность циклов |

MODE[3:0] |

DATA[15:0] и DATA[8:0] |

| 1 |

Цикл записи |

CMDE |

GVE |

| 2 |

Цикл записи |

DATA |

Версия FFPI |