Команда FMUL - Дробное незнаковое умножение

Описание:

Эта инструкция выполняет 8-бит x 8-бит --> 16-бит знаковое умножение и сдвиг результата на 1 бит влево.

Пусть (N.Q) обозначают дробное число с N двоичных цифр слева от точки, и Q двоичных цифр справа от точки. Умножение между двумя числами в форматах (N1.Q1) и (N2.Q2) даст результат в формате ((N1 + N2). (Q1 + Q2)).

Формат (1.7) широко используется как входные числа для сигнальной обработки, а получившийся в результате формат (2.14) - как результат. Сдвиг влево необходим для того, что бы старший байт результата был в таком же формате как входные числа. Инструкция FMULS, включая операцию сдвига, выполняется за такое же число циклов как инструкция MUL.

Формат (1,7) наиболее широко используется со знаковыми числами, а инструкция FMUL выполняет незнаковое умножение. Эта инструкция наиболее полезна при вычислении части результата при выполнении умножения со знаком 16-битных чисел в формате (1.15), дающие результат в формате (1,31).

Примечание: результат операции FMUL может подвергнуться двойному переполнению, если интерпретировать число в формате (1.15). MSB умножения, до сдвига, должно быть учтено, и находится в бите переноса. См. следующий пример.

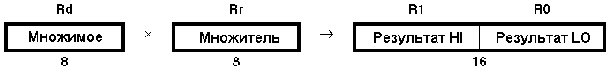

Rd множимое и множитель Rr - два регистры, содержащие незнаковые дробные числа, у которых мнимая точка расположена между битом 6 и битом 7.

16-битный знаковый дробный результат с мнимой точкой между битом 14 и битом 15 помещается в R1 (старший байт) и R0 (младший байт).

Эта инструкция не доступна во всех устройствах. Обратитесь к сводной инструкции конкретного устройства.

Операция:

| (i) |

R1:R0 <- Rd x Rr (незнаковое (1.15) <- незнаковое (1.7) x незнаковое (1.7)) |

| |

| |

Синтаксис |

Операнды: |

Счетчик программ: |

| (i) |

FMUL Rd,Rr |

16  d d  23, 16 23, 16  r r  23 23 |

PC <- PC + 1 |

16-разрядный код операции:

Булевы выражения регистра статуса (SREG)

C: R16

Установлен, если бит 15 результата до сдвига в лево установлен, очищен в ином случае.

Z: R15 · R14 · R13 · R12 · R11 · R10 · R9 · R8 · R7 · R6 · R5 · R4 · R3 · R2 · R1 · R0

Установлен, если результат равен $0000, очищен в ином случае.

Пример:

;******************************************************************************

;* ОПИСАНИЕ

;*Знаковое дробное умножение двух 16 битных чисел с 32 битным результатом.

;* Используются:

;*r19:r18:r17:r16 = ( r23:r22 * r21:r20 ) << 1

;******************************************************************************

fmuls16x16_32:

clrr2

fmulsr23, r21;((знаковое)ah * (знаковое)bh) << 1

movwr19:r18, r1:r0

fmulr22, r20;(al * bl) << 1

adcr18, r2

movwr17:r16, r1:r0

fmulsur23, r20;(( знаковое)ah * bl) << 1

sbcr19, r2

addr17, r0

adcr18, r1

adcr19, r2

fmulsur21, r22;(( знаковое)bh * al) << 1

sbcr19, r2

addr17, r0

adcr18, r1

adcr19, r2

Слов: 1 (2 байта)

Циклов:2

|