30.5 Функциональное описание

30.5.1 Формат передачи

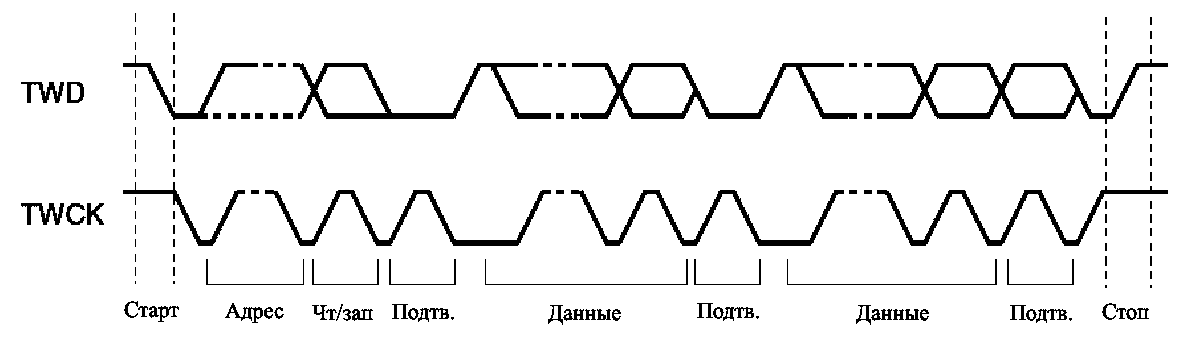

Выдаваемые на линию TWI данные должны иметь 8-битный формат. Первым передается СЗБ, прием каждого байта информации сопровождается подтверждением. Количество байт в передаче не ограничено (см. Рис. 30-4).

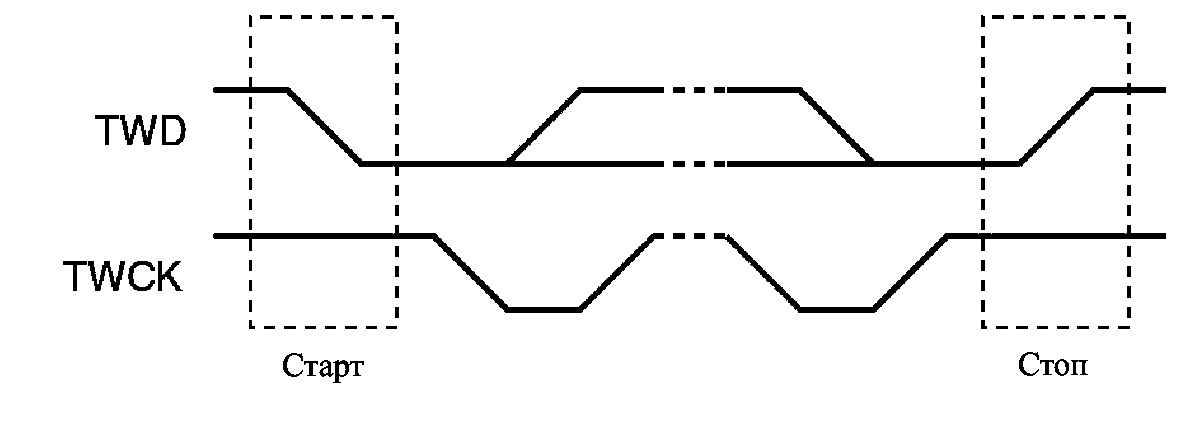

Каждая передача начинается с условия Старт и заканчивается условием Стоп (см. рис. 30-4).

- Перепад высокий - низкий уровень на линии TWD при высоком уровне на TWCK определяется как условие Старт.

- Перепад низкий - высокий на линии TWD при высоком уровне на TWCK определяется как условие Стоп.

Рис. 30-3. Условия Старт и Стоп

Рис. 30-4. Формат передачи

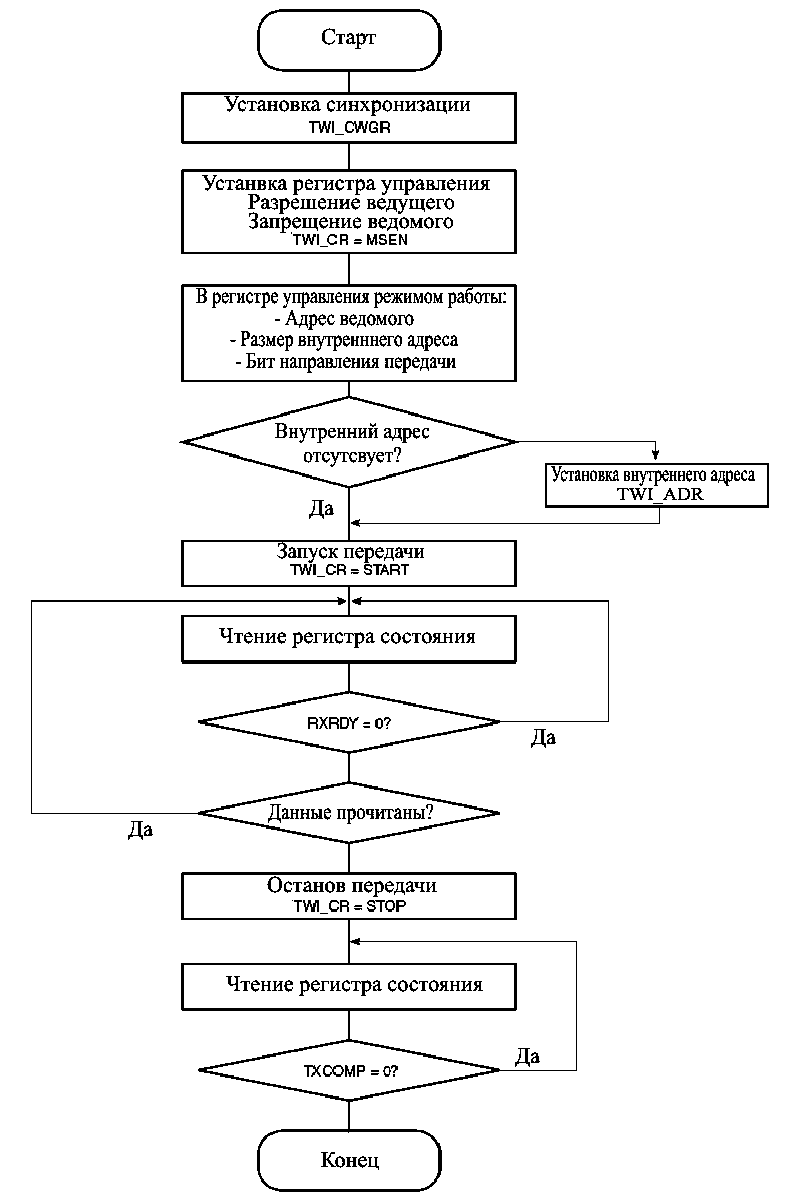

30.5.2 Режимы работы

Двухпроводной интерфейс имеет два режима работы:

- Режим ведущего устройства - передатчика

- Режим ведущего устройства - приемника

Регистр управления (TWI_CR) дает возможность конфигурировать двухпроводной интерфейс в режиме ведущего. В этом режиме он генерирует частоту синхронизации в соответствии со значением, запрограммированным в Регистре формы сигнала синхронизации (TWI_CWGR). Этот регистр позволяет полностью определить параметры сигнал TWCK, позволяя интерфейсу работать в широком диапазоне тактовых частот.

30.5.3 Передача данных

После установки ведущим устройством условия Старт оно отсылает 7-битный адрес ведомого устройства, заданный в регистре Режима работы (DADR в TWI_MMR). Следующий за передачей адреса бит определяет направление передачи данных - прием или передача. Равенство этого бита 0 показывает, что будет осуществляться запись данных (операция передачи). Если же бит равен 1, запрашивается чтение данных (операция чтения).

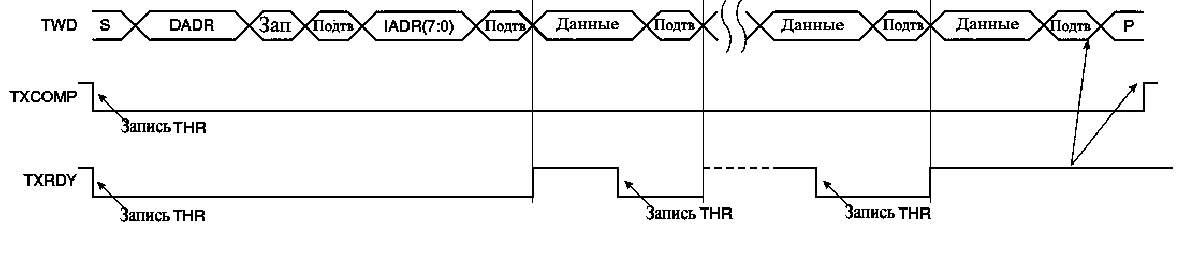

Для работы двухпроводного интерфейса необходимо получение подтверждения о принятии каждого байта от ведомого устройства. Во время тактового импульса синхронизации, совпадающего с ожиданием подтверждения, ведущее устройство освобождает управление линией данных (на ней устанавливается высокий уровень), с тем, чтобы ведомое устройство могло установить на ней низкий уровень, выдавая таким образом уровень подтверждения. Ведущее устройство опрашивает линию данных во время этого импульса синхронизации, устанавливая бит NAK в Регистре состояния в случае, если ведомое устройство не выдало на линию сигнал подтверждения. Установка этого бита, как и некоторых других бит состояния, может генерировать прерывания, если это разрешено соответствующими установками в регистре разрешения прерываний интерфейса (TWI_IER). Передача начинается после записи в регистр хранения передачи (TWI_THR) и установки бита Старт в регистре управления. Данные последовательно выдаются на линию встроенным сдвиговым регистром, и при получении сигнала подтверждения производится установка бита TXRDY, который имеет высокий уровень до тех пор, пока не производится новая запись в регистр TWI_THR (см. Рис. 30-6). При завершения передачи ведущее устройство выдает на линию условие Стоп.

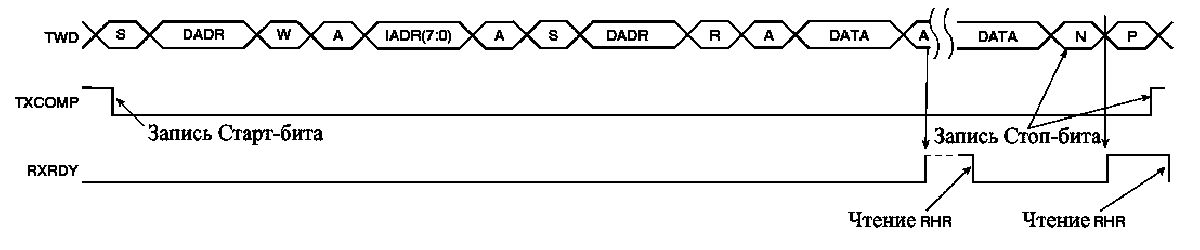

Последовательность чтения начинается установкой Старт-бита. При установке в 1 бита RXRDY в регистре состояния начинается прием пакет данных в регистр хранения приема (TWI_RHR). При считывании этого регистра бит RXRDY регистра TWI_RHR сбрасывается.

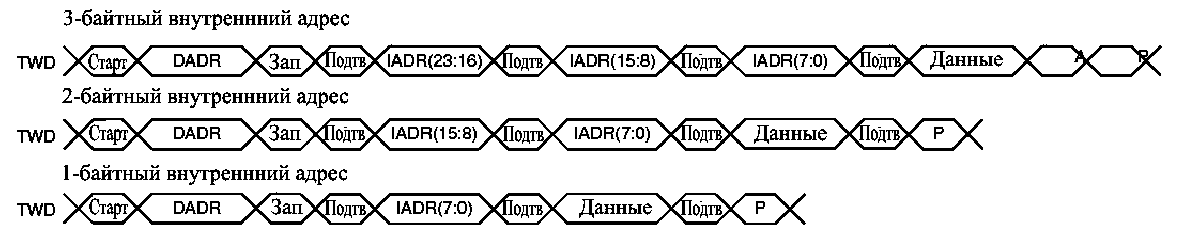

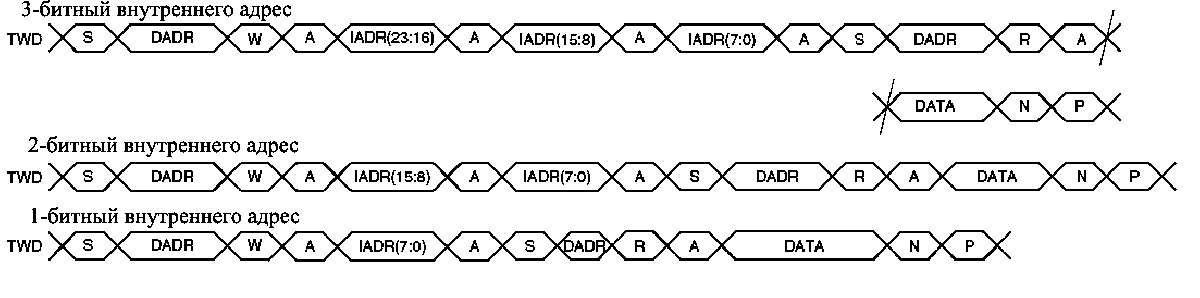

Двухпроводной интерфейс предоставляет возможность осуществлять передачу в различных форматах (7-битный адрес ведомого или 10-битный адрес ведомого). Три внутренних адресных бита можно конфигурировать с помощью регистра режима работы ведущего устройства (TWI_MMR). Если ведомое устройство поддерживает только 7-битную адресацию, IASDR должен быть установлен в 0. Для адреса ведомого более 7 бит, пользователь должен сконфигурировать размер адреса (IADRSZ) и установить другой адрес ведомого в регистре внутреннего адреса.

Рис. 30-5. Запись ведущим устройством с одним, двумя или тремя байтами внутреннего адреса и одним байтом данных

Рис. 30-6. Запись ведущим устройством с одним байтом внутреннего адреса и несколькими байтами данных

Рис. 30-7. Чтение ведущим устройством с одним, двумя или тремя байтами внутреннего адреса и одним байтом данных

Рис. 30-8. Чтение ведущим устройством с одним байтом внутреннего адреса и несколькими байтами данных

- S = Старт

- P = Стоп

- W = Запись

- R = Чтение

- A = Подтверждение

- N = Отсутствие подтверждения

- DADR = Адрес устройства

- IADR = Внутренний адрес

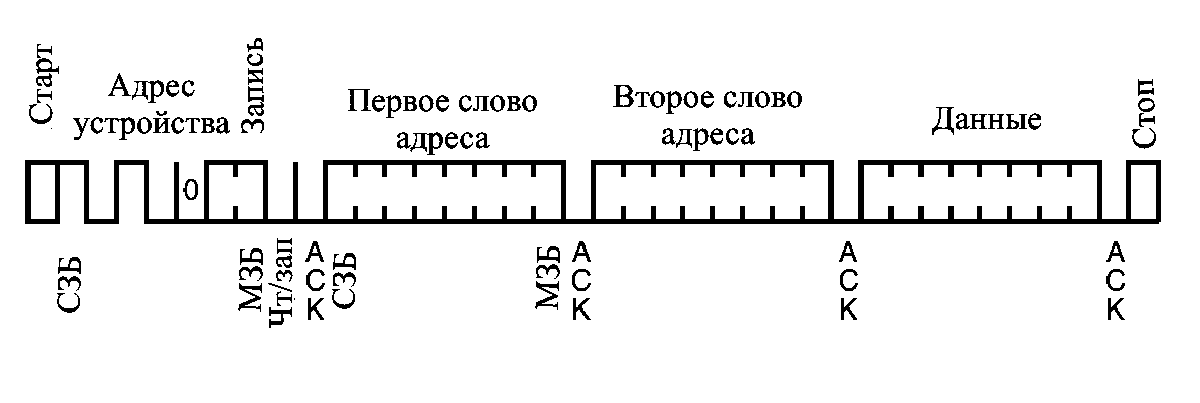

Рис. 30-9 показывает запись байта данных в ЭСППЗУ Atmel AT24LC512 (EEPROM). Показано применение внутреннего адреса для доступа у к устройству.

Рис. 30-9. Использование внутреннего адреса

30.5.4 Диаграммы чтения/записи

Диаграммы, показанные на рис. 30-10 и 30-11, показывают примеры чтения и записи в режиме ведущего устройства. Для проверки бит состояния могут применяться как программный опрос, так применение прерываний. Для метода с использованием прерываний необходимо в первую очередь сконфигурировать регистр разрешения прерываний (TWI-IER).

Рис. 30-10 Запись в режиме ведущего

Рис. 30-11. Чтение в режиме ведущего

|