29.7 Пользовательский интерфейс последовательно - параллельного интерфейса (SPI)

Табл. 29-3. Карта регистров ППИ

| Смещение |

Регистр |

Название регистра |

Доступ |

Значение после перезагрузки |

| 0x00 |

Регистр управления |

SPI_CR |

Только запись |

- |

| 0x04 |

Регистр установки режима |

SPI_MR |

Чтение/запись |

0x0 |

| 0x08 |

Регистр данных приемника |

SPI_RDR |

Только чтение |

0x0 |

| 0x0C |

Регистр данных передатчика |

SPI_TDR |

Только запись |

- |

| 0x10 |

Регистр состояния |

SPI_SR |

Только чтение |

0x000000F0 |

| 0x14 |

Регистр разрешения прерываний |

SPI_IER |

Только запись |

- |

| 0x18 |

Регистр запрещения прерываний |

SPI_IDR |

Только запись |

- |

| 0x1C |

Регистр маски прерываний |

SPI_IMR |

Только чтение |

0x0 |

| 0x20 - 0x2C |

Зарезервировано |

- |

- |

- |

| 0x30 |

Регистр выбора корпуса 0 |

SPI_CSR0 |

Чтение/запись |

0x0 |

| 0x34 |

Регистр выбора корпуса 1 |

SPI_CSR1 |

Чтение/запись |

0x0 |

| 0x38 |

Регистр выбора корпуса 2 |

SPI_CSR2 |

Чтение/запись |

0x0 |

| 0x3C |

Регистр выбора корпуса 3 |

SPI_CSR3 |

Чтение/запись |

0x0 |

| 0x004C - 0x00F8 |

Зарезервировано |

- |

- |

- |

| 0x004C - 0x00FС |

Зарезервировано |

- |

- |

- |

| 0x100 - 0x124 |

Зарезервировано для Периферийного ПДП контроллера |

- |

- |

- |

29.7.1 Регистр управления Последовательным периферийным интерфейсом.

Название: SPI_CR

Вид доступа: Только запись

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| - |

- |

- |

- |

- |

- |

- |

LASTXFER |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| SWRST |

- |

- |

- |

- |

- |

SPIDIS |

SPIEN |

- SPIEN: разрешение работы интерфейса

- 0 =Не влияет.

- 1 = Разрешает интерфейсу прием и передачу данных.

- SPIDIS: Запрещение работы интерфейса

- 0 =Не влияет.

- 1 = Запрещает интерфейс.

- SWRST: Перезагрузка интерфейса программными средствами

- 0 =Не влияет

- 1 = Перезагружает интерфейс. Происходит программно запускаемая аппаратная перезагрузка интерфейса SPI.

- LASTXFER: Последняя передача

- 0 =Не влияет.

- 1 = Текущий активный вывод NPCS будет снят после того, как завершится передача пакета, записанного TD. Если при установленном бите CSAAT осуществляется возможность сразу же отключить текущее периферийное устройство, сразу же, без задержки после завершения передачи установив высокий уровень соответствующего NPCS после завершения передачи.

29.7.2 Регистр выбора режима работы

Название: SPI_MR

Вид доступа: Запись/чтение

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| DLY BCS |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

PCS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| LLB |

- |

- |

MODFDIS |

- |

PCSDEC |

PS |

MSTR |

- MSTR: Режим ведущий/ведомый

- 0 =Интерфейс работает в режиме ведомого.

- 1 = Интерфейс работает в режиме ведущего.

- PS: Выбор периферийного устройства

- 0 = Фиксированный выбор корпуса внешнего периферийного устройства.

- 1 = Изменяемый выбор периферийного устройства.

- PCSDEC: Декодирование выбора корпуса

- 0 = Периферийные устройства непосредственно подключены к выводам выбора корпуса.

- 1 = Четыре вывода выбора корпуса подключаются к дешифрирующей логике для выдачи сигнала разрешения работы на одно из 16 (максимум) устройств.

SPI_CSR0 определяет сигналы выбора корпуса от 0 до 3.

SPI_CSR1 определяет сигналы выбора корпуса от 4 до7.

SPI_CSR2 определяет сигналы выбора корпуса от 8 до 11.

SPI_CSR3 определяет сигналы выбора корпуса от 12 до14. |

- MODFDIS: Определение ошибки режима работы

- 0 =Определение ошибки режима работы запрещено.

- 1 = Определение ошибки режима работы разрешено.

- LLB: Разрешение местного зацикливания

- 0 = Работа петли местного зацикливания запрещена.

- 1 = Работа петли местного зацикливания разрешена.

- PCS: Выбор корпуса периферии

Применяется только в том случае, если используется фиксированный выбор периферии (PS=0).

Если PCSDEC = 0, то:

PCS = xxx0 NPCS[3;0] = 1110

PCS = xx01 NPCS[3:0] = 1101

PCS = x011 NPCS[3:0] = 1011

PCS = 0111 NPCS[3:0] = 0111

PCS = 1111 запрещено (ни одно периферийное устройство не выбрано)

(знаком "x" отмечены поля, данные в которых не имеют значения)

Если PCSDEC = 1, то:

Выходные сигналы NPCS[3:0] соответствуют значению PCS.

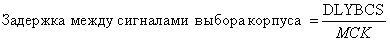

- DLYBCS: Задержка между сигналами выбора корпуса

Это поле определяет значение задержки между переходом от неактивного состояния одной линии NPCS к активному состоянию другой линии NPCS. Задержка по времени гарантирует то, что сигналы выбора корпуса не перекроются по времени, и устранит возможную конкуренцию при работе на шине, возможную в случае, если периферийные устройства имеют значительное время преобразования.

Если значение DLYBCS равно или менее шести, шесть периодов MCK будут вставлены по умолчанию.

Во всех прочих случаях значение задержки определяется следующим уравнением:

29.7.3 Регистр данных приемника ППИ (SPI)

Название: SPI_RDR

Тип доступа: Только чтение

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

PCS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| RD |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| RD |

- RD: Принятые данные

Данные, принятые ППИ (SPI) - интерфейсом, хранятся в этом регистре с выравниванием по правой стороне. В неиспользованные биты записывается нулевое значение.

- PCS: Выбор корпуса внешних устройств

В режиме ведущего эти биты показывают значение на выводах NPCS в конце цикла передачи. Во всех других случаях чтение возвращает нулевое значение.

29.7.4 Регистр данных передатчика ППИ (SPI)

Название: SPI_TDR

Тип доступа: Только запись

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| - |

- |

- |

- |

- |

- |

- |

LASTXFER |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

PCS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| TD |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| TD |

- RD: Передаваемые данные

Данные, предназначенные для передачи ППИ (SPI) - интерфейсом, хранятся в этом регистре. Информация, предназначенная для передачи, должна быть записана в этот регистр с выравниванием по правой стороне.

- PCS: Выбор корпуса периферии

Это поле используется только в том случае, если режим переменного вида корпуса периферии активен (PS=1).

Если PCSDEC = 0:

PCS = xxx0 NPCS[3;0] = 1110

PCS = xx01 NPCS[3:0] = 1101

PCS = x011 NPCS[3:0] = 1011

PCS = 0111 NPCS[3:0] = 0111

PCS = 1111 запрещено (ни одно периферийное устройство не выбрано)

(знаком "x" отмечены поля, данные в которых не имеют значения)

Если PCSDEC = 1, то:

Выходные сигналы NPCS[3:0] соответствуют значению PCS.

- LASTXFER: Последняя передача

- 0 = Не влияет.

- 1 = Активный уровень текущей линии NPCS будет снят после того, как будет завершена передача пакета, записанного в регистр TD. При установленном бите CSAAT активный (низкий) уровень соответствующей линии NPCS будет снят сразу же после завершения передачи.

Это поле используется только в том случае, если установлен переменный выбор корпуса периферии.

29.7.5 Регистр состояния ППИ (SPI)

Название: SPI_SR

Тип доступа: Только чтение

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

SPIENS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| - |

- |

- |

- |

- |

- |

TXEMPTY |

NSSR |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| TXBUFE |

RXBUFF |

ENDTX |

ENDRX |

OVRES |

MODF |

TDRE |

RDRF |

- RDRF: Переполнение приемного регистра хранения данных ППИ

- 0 = C момента последнего чтения SPI_RDR не было принято данных

- 1 = Данные были приняты и принятые данные переданы из последовательно - параллельного преобразователя в SPI_RDR с момента последнего чтения SPI_RDR

- TDRE: Опустошение передающего регистра

- 0 = Данные были записаны в SPI_TDR но еще не переданы в параллельно - последовательный преобразователь.

- 1 = Последние записанные в регистр хранения передачи данные уже переданы в параллельно - последовательный преобразователь.

- MODF: Ошибка режима работы

- 0 = Ошибка режима не была определена с момента последнего чтения регистра состояния ППИ (SPI_SR).

- 1 = С момента последнего чтения регистра состояния ППИ была обнаружена ошибка режима работы интерфейса.

- OVRES: Состояние ошибки переполнения

- 0 = С момента последнего чтения регистра состояния не было обнаружено ошибок переполнения.

- 1 = С момента последнего чтения регистра состояния была обнаружена ошибка переполнения.

Ошибкой считается состояние, когда в SPI_RDR (регистр хранения принимаемых данных) были загружены данные из последовательно - параллельного преобразователя как минимум два раза без чтения.

- ENDRX: Конец (опустошение) буфера передачи (RX)

- 0 = Регистр - счетчик приемника не осуществил счет до 0 с момента последней записи в SPI_RCR или SPI_RNCR.

- 1 = Регистр - счетчик приемника досчитал до 0 с момента последней записи в SPI_RCR или SPI_RNCR.

- ENDTX: Конец (завершение) буфера приема (TX)

- 0 = Регистр - счетчик передатчика не осуществил счет до 0 с момента последней записи в SPI_RCR или SPI_RNCR.

- 1 = Регистр - счетчик передатчика досчитал до 0 с момента последней записи в SPI_RCR или SPI_RNCR.

- RXBUFF: Буфер приемника заполнен

- 0 = SPI_RCR(1) или SPI_RNCR(1) содержат значение, отличное от 0.

- 1 = SPI_RCR(1) и SPI_RNCR(1) оба имеют нулевое значение.

- TXBUFE: Буфер передатчика опустошен

- 0 = SPI_TCR(1) или SPI_TNCR(1) содержат значение, большее, чем 0.

- 1 = SPI_TCR(1) и SPI_TNCR(1) оба имеют нулевое значение.

- NSSR: Изменение уровня на ножке NSS

- 0 = С момента последнего чтения не было определено изменение уровня (переход высокий - низкий, фронт) на ножке NSS.

- 1 = С момента последнего чтения было определено изменение уровня на ножке NSS.

- TXEMPTY: Опустошение регистров передачи

- 0 = Устанавливается сразу же после записи данных в SPI_TDR.

- 1 = SPI_TDR и регистр сдвига опустошены. Если была установлена задержка передачи, TXEMPTY устанавливается после ее завершения.

- SPIENS: Состояние разрешения SPI

- 0 = ППИ (SPI) запрещен.

- 1 = ППИ (SPI) разрешен.

Заметка: SPI_RCR, SPI_RNCR, SPI_TCR, SPI_TNCR физически размещены в контроллере прямого доступа к памяти периферийных модулей (PCD).

29.7.6 Регистр разрешения прерываний ППИ

Название: SPI_IER

Тип доступа: Только запись

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| - |

- |

- |

- |

- |

- |

TXEMPTY |

NSSR |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| TXBUFE |

RXBUFF |

ENDTX |

ENDRX |

OVRES |

MODF |

TDRE |

RDRF |

- RDRF: Разрешение прерывания по переполнению приемного регистра хранения данных ППИ

- TDRE: Разрешении переполнения по опустошению передающего регистра

- MODF: Разрешение прерывания по ошибке режима работы

- OVRES: Разрешение прерывания по состоянию ошибки переполнения

- ENDRX: Разрешение прерывания по опустошению буфера передачи (RX)

- ENDTX: Разрешение прерывания по опустошению буфера приема (TX)

- RXBUFF: Разрешение прерывания по заполнению буфер приемника

- TXBUFE: Разрешение прерывания по опустошению буфера передатчика

- TXEMPTY: Разрешение прерывания по опустошению регистров передачи

- NSSR: Разрешение прерывания по изменению уровня на ножке NSS

- 0 = не влияет

- 1 = разрешает соответствующее прерывание

29.7.7 Регистр запрещения прерываний ППИ (SPI)

Название: SPI_IDR

Тип доступа: Только запись

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| - |

- |

- |

- |

- |

- |

TXEMPTY |

NSSR |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| TXBUFE |

RXBUFF |

ENDTX |

ENDRX |

OVRES |

MODF |

TDRE |

RDRF |

- RDRF: Запрещение прерывания по переполнению приемного регистра хранения данных ППИ

- TDRE: Запрещение переполнения по опустошению передающего регистра

- MODF: Запрещение прерывания по ошибке режима работы

- OVRES: Запрещение прерывания по состоянию ошибки переполнения

- ENDRX: Запрещение прерывания по опустошению буфера передачи (RX)

- ENDTX: Запрещение прерывания по опустошению буфера приема (TX)

- RXBUFF: Запрещение прерывания по заполнению буфер приемника

- TXBUFE: Запрещение прерывания по опустошению буфера передатчика

- TXEMPTY: Запрещение прерывания по опустошению регистров передачи

- NSSR: Запрещение прерывания по изменению уровня на ножке NSS

- 0 = не влияет

- 1 = запрещает соответствующее прерывание

29.7.8 Регистр маски прерываний

Название: SPI_IMR

Тип доступа: Только чтение

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| - |

- |

- |

- |

- |

- |

TXEMPTY |

NSSR |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| TXBUFE |

RXBUFF |

ENDTX |

ENDRX |

OVRES |

MODF |

TDRE |

RDRF |

- RDRF: Маска прерывания по переполнению приемного регистра хранения данных ППИ

- TDRE: Маска прерывания по опустошению передающего регистра

- MODF: Маска прерывания по ошибке режима работы

- OVRES: Маска прерывания по состоянию ошибки переполнения

- ENDRX: Маска прерывания по опустошения буфера передачи (RX)

- ENDTX: Маска прерывания по опустошению буфера приема (TX)

- RXBUFF: Маска прерывания по заполнению буфера приемника

- TXBUFE: Маска прерывания по заполнению буфера передатчика

- TXEMPTY: Маска прерывания по опустошению регистров передачи

- NSSR: Маска прерывания по изменению уровня на ножке NSS

29.7.9 Регистр выбора корпуса ППИ (SPI)

Название: SPI_CSR0…SPI_CSR3

Тип доступа: Чтение/запись

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| DLYBCT |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| DLYBS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| SCBR |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| BITS |

CSAAT |

- |

NCPHA |

CPOL |

- CPOL: полярность синхронизирующего сигнала

- 0 = Уровень неактивного состояния синхронизации передачи данных по ППИ соответствует логическому нулю.

- 1 = Уровень неактивного состояния синхронизации передачи данных по ППИ соответствует логической единице.

CPOL применяется для определения неактивного состояния синхронизации передачи ППИ (SPCK). Это поле используется совместно с NCPHA для установки необходимого для работы с ведомым устройством сочетания значений синхронизирующего сигнала и формата передачи данных.

- NCPHA: Фаза синхронизирующего сигнала

- 0 = Данные изменяются (выдаются) по переднему фронту SPCK и принимаются по заднему фронту (по фронту и срезу).

- 1 = Данные принимаются по переднему фронту SPCK и выдаются по заднему фронту.

Поле NCPHA определяет, какой из перепадов синхронизирующего сигнала запускает передачу и какой - прием данных. Это поле используется совместно с CPOL для установки необходимого для работы с ведомым устройством сочетания значений синхронизирующего сигнала и формата передачи данных.

- СCSAAT: Активность линии выбора корпуса после завершения передачи

- 0 = Высокий (неактивный) уровень линии выбора корпуса периферийного устройства устанавливается сразу же после окончания передачи.

- 1 = Низкий (активный) уровень линии выбора корпуса периферийного устройства удерживается после окончания передачи. Он удерживается до тех пор, пока не начнется передача с выбором корпуса внешнего устройства по другой линии.

- BITS: Количество бит данных в пакете

Это поле определяет количество бит данных, передаваемых в одном пакете. Зарезервированные значения поля не должны использоваться.

| BITS |

Количество бит данных |

| 0000 |

8 |

| 0001 |

9 |

| 0010 |

10 |

| 0011 |

11 |

| 0100 |

12 |

| 0101 |

13 |

| 0110 |

14 |

| 0111 |

15 |

| 1000 |

16 |

| 1001 |

Зарезервировано |

| 1010 |

Зарезервировано |

| 1011 |

Зарезервировано |

| 1100 |

Зарезервировано |

| 1101 |

Зарезервировано |

| 1110 |

Зарезервировано |

| 1111 |

Зарезервировано |

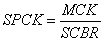

- SBCR: Скорость последовательной передачи данных

В режиме ведущего устройства ППИ - интерфейс использует счетчик по модулю для получения значения скорости последовательной передачи данных из главной синхронизации. Значение тактовой частоты передачи данных устанавливается записью в поле SBCR значения от 1 до 255. Значение тактовой частоты передачи данных определяется выражением:

Запись нулевого значения в поле SCBR запрещена. Запуск передачи данных при записанном в SCBR нуле может привести к непредсказуемым сбоям в работе устройства. Значение SCBR по умолчанию также составляет 0, поэтому после пользователь перед осуществлением передачи должен программно изменить его значение на допустимое.

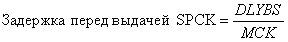

- DLYBS: Задержка перед выдачей тактовой частоты ППИ (SPCK)

Это поле определяет значение задержки, которая отделяет начало выдачи тактовой частоты передачи данных установления от выдачи уровня NPCS.

Если DLYBS равен нулю, выдача тактовой частоты передачи данных (SPCK) начнется через половину ее периода после установления уровня NPCS.

В прочих случаях значение задержки определяется выражением:

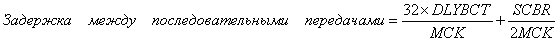

- DLYBCT: Задержка между последовательными передачами данных

Это поле определяет значение задержки между двумя последовательными передачами данных с одним и тем же периферийным устройством без снятия уровня выбора корпуса. Это время выдерживается каждый после каждой осуществленной передачи, и, при необходимости, перед снятием уровня выбора корпуса.

При значении DLYBCT, равном нулю, никакой задержки между последовательными передачами не происходит и синхронизация передачи данных продолжается после завершения передачи пакетов.

В прочих случаях значение задержки определяется следующим выражением:

|