26. Контроллер управления потребляемой мощности (PMC)

26.1 Описание

Контроллер управления потребляемой мощности (PMC) оптимизирует потребление мощности, управляя всеми системными и периферийными тактовыми сигналами. PMC разрешает/запрещает подачу тактовых сигналов на входы многих периферийных модулей и ARM ядра.

Контроллер управления потребляемой мощности использует выходы тактового генератора для формирования следующих синхронизирующих сигналов:

- главный синхронизирующий сигнал (MCK), программируется от нескольких сотен герц до максимальной рабочей частоты. Имеется возможность постоянной работы модулей, таких как контроллер прерываний и диспетчер памяти.

- синхронизирующий сигнал процессора (PCK), сигнал отключается, когда процессор переходит в холостой режим работы

- независимые синхронизирующие сигналы периферийных модулей (USART, SSC, SPI,TWI, TC, MCI,), обычно сигнал MCK. Для упрощения все синхронизирующие сигналы периферийных модулей обозначены МСК.

- синхронизирующий сигнал USB порта (UDPCK), кроме AT91SAM7S32;

- три программно управляемых внешних тактовых выхода.

26.2 Контроллер главного синхронизирующего сигнала (Master Clock Controller)

Контроллер главного синхронизирующего сигнала осуществляет выбор и формирование основного тактового сигнала MCK (Master Clock). Тактовый сигнал MCK поступает на все периферийные модули и на контроллер памяти.

Сигнал MCK формируется одним из тактовых сигналов с выхода тактового генератора (Clock Generator). При выборе сигнала SLCK для сигнала MCK весь микроконтроллер тактируется низкочастотным сигналом SLCK. При выборе сигнала MAINCK схема ФАПЧ отключена, что уменьшает энергопотребление.

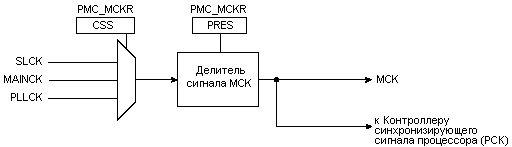

Контроллер главного синхронизирующего сигнала состоит из переключателя тактовых сигналов и делителя.

Выбор сигнала MCK осуществляется записью поля CSS (Clock Source Selection) регистра основного тактового сигнала PMC_MCKR (Master Clock Register). Делитель поддерживает деление на значение 2 в степени, в диапазоне от 1 до 64. Поле PRES регистра PMC_MCKR определяет значение предделителя.

Каждый раз при записи регистра PMC_MCKR для определения нового значения для сигнала MCK, очищается MCKRDY бит в регистре PMC_SR. Этот бит считывается нулем до тех пор, пока сигнал MCK не установится. После этого MCKRDY бит устанавливается, и может вызвать прерывание ядра. Эта особенность полезна при переключении с тактового сигнала высокой частоты на сигнал более низкой частоты, сообщая программе о том, что изменения вступили в силу.

Рис. 26-1. Контроллер главного синхронизирующего сигнала

26.3 Контроллер синхронизирующего сигнала процессора

Контроллер синхронизирующего сигнала процессора определяет холостой режим процессора. Синхронизирующий сигнал процессора разрешается и запрещается записью в регистр разрешения системного тактового сигнала PMC_SCER (System Clock Enable Register) и в регистр запрета системного тактового сигнала PMC_SCDR (System Clock Enable Register) соответственно. Состояние этого тактового сигнала (например, для режима отладки) считывается из регистра статуса системного тактового сигнала PMC_SCSR (System Clock Status Register).

Сброс или любое разрешенное прерывание разрешает работу тактового сигнала PCK. Переход в холостой режим осуществляется запрещением сигнала PCK.

После запрещения сигнала PCK текущая исполняемая команда выполняется до остановки тактового сигнала, но это не влияет на пересылку данных от других управляющих узлов системной шины.

26.4 Контроллер синхронизирующего сигнала USB

Примечание: В AT91SAM7S32 Контроллер синхронизирующего сигнала USB отсутствует.

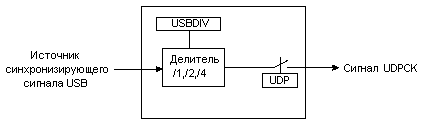

Источник синхронизирующего сигнала USB - выход ФАПЧ. При использовании USB схему ФАПЧ необходимо запрограммировать на формирование сигнала частотой 48 МГц, 96 МГц или 192 МГц. Точность установки частоты должна составлять 0,25%., зависящая от USBDIV бита в регистре CKGR_PLLR.

После появления стабильного сигнала на выходе ФАПЧ LOCK бит будет установлен.

- Синхронизирующий сигнал USB разрешается установкой UDP бита регистра PMC_SCER. Для уменьшения потребления, если не используется модуль USB, необходимо установить UDP бит регистра PMC_SCDR. Бит UDP регистра PMC_SCSR разрешает работу этого тактового сигнала. Для работы периферийного модуля USB требуется два тактовых сигнала: сигнал частотой 48 МГц и сигнал MCK. Сигнал MCK может управляться контроллером тактовых сигналов периферийных модулей (Peripheral Clock Controller).

Рис. 26-2. Контроллер синхронизирующего сигнала USB

|