24.7 Функциональное описание

24.7.1 Управление источником прерывания

24.7.1.1 Режим источника прерывания

Контроллер прерываний работает независимо с каждым источником прерывания. Поле SRC-TYPE соответствующего регистра режима прерывания AIC_SMR (Source Mode Register) задает условия для каждого источника прерывания.

Внутренние источники прерываний, подключенные к выходам встроенных периферийных модулей, могут быть запрограммированы на срабатывание, как по уровню, так и по изменению уровня. Значения активных уровней внутренних прерываний для пользователя не имеют значения.

Источники внешних прерываний могут быть запрограммированы на срабатывание по фронту (нарастающий или спадающий), а также по низкому или высокому уровню сигнала.

24.7.1.2 Разрешение источника прерывания

Каждое прерывание, включая FIQ 0-ого источника, может быть разрешено или запрещено через управляющие регистры: регистр разрешения прерывания AIC_IECR (Interrupt Enable Command Register) и регистр запрещения прерывания AIC_IDCR (Interrupt Disable Command Register). Установки этих регистров выполняются одной командой. Чтение маски прерываний производится через регистр AIC_IMR. Запрещенное прерывание не оказывает влияния на обработку других прерываний.

24.7.1.3 Установка и сброс прерывания

Все встроенные источники прерываний, запрограммированные на срабатывание по изменению уровня (включая FIQ 0-ого источника), могут быть индивидуально установлены или сброшены записью соответственно в регистры AIC_ISCR и AIC_ICCR. Сброс или установка источника прерывания, запрограммированного на срабатывание по уровню, не приводит к возникновению соответствующего прерывания.

Операция очистки прерывания некорректна, так как программа должна произвести вновь инициализацию схемы "с памятью", активированной после того как источник прерывания запрограммирован на срабатывание по фронту. Операция установки прерывания может быть использована для самотестирования или программной отладки. Также эта операция может быть использована для реализации обработки программного прерывания.

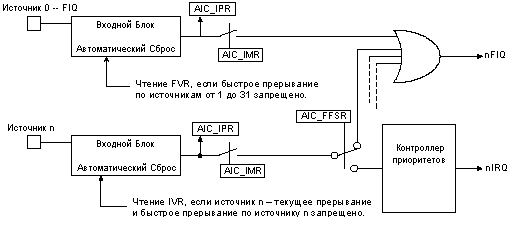

Особенность контроллера прерывания - автоматический сброс текущего прерывания после чтения регистра вектора прерывания AIC_IVR (Interrupt Vector Register). Этой операции подвергается только источник прерывания определенный контроллером прерывания AIC как текущее прерывание (см. "Контроллер приоритетов" на стр. 157). Автоматический сброс уменьшает количество требуемых операций в процедуре обработки прерывания, чтобы прочитать регистр AIC_IVR. Отметим, что автоматический сброс прерывания невозможен для источника прерывания, для которого включен режим эмуляции быстрого прерывания, так как в этом случае он рассматривается как источник FIQ (см. "Эмуляция быстрого прерывания" на стр.161).

Автоматический сброс 0-го источника прерывания выполняется после чтения регистра AIC_FVR.

24.7.1.4 Статус прерывания

Для каждого прерывания действия контроллера прерываний AIC изменяют регистр обрабатываемого прерывания AIC_IPR (Interrupt Pending Register) и регистр маски прерывания AIC_IMR (Interrupt Mask Register). Регистр AIC_IPR разрешает работу источников прерывания, независимо от того маскирован он или нет.

Регистр AIC_ISR считывает номер текущего прерывания (см. "Контроллер приоритетов" стр. 157), регистр AIC_CISR выдает образы сигналов nIRQ и nFIQ, поступающие на ядро ARM.

Регистры, описанные выше, могут быть использованы для оптимизации обработки прерываний системы.

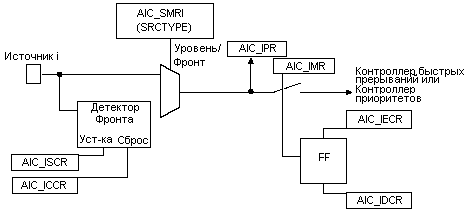

24.7.1.5 Внутренняя структура источника внутренних прерываний

Рис. 24-4. Внутренняя структура источника внутренних прерываний

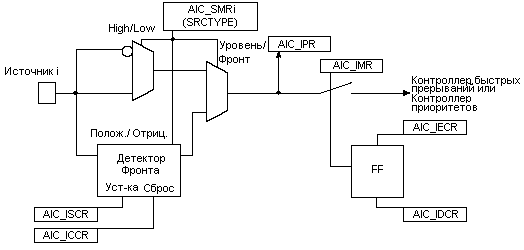

24.7.1.6 Внутренняя структура источника внешних прерываний

Рис. 24-5. Внутренняя структура источника внешних прерываний

24.7.2 Задержки прерываний

Задержки вызова прерываний зависят от нескольких параметров:

- Время программного маскирования прерываний;

- Время срабатывания, как на стороне ядра, так и на стороне контроллера прерываний;

- Время исполнения команды при срабатывании прерывания;

- Время обработки прерывания более высокого приоритета и ресинхронизация сигналов в контроллере.

В этой части описана только ресинхронизация сигналов. Она подробно описывает временные задержки с момента приема запроса внешнего прерывания (по уровню или по изменению уровня) или срабатывания внутреннего источника прерывания и появлением сигналов nIRQ или nFIQ на входах ядра. Время ресинхронизации зависит от программирования источника прерывания и его типа (внутренне или внешнее). Для стандартного прерывания время ресинхронизации дается в предположении отсутствия появления прерывания повышенного приоритета.

Переключение контроллера портов ввода вывода не влияет на задержки прерываний от внешних источников.

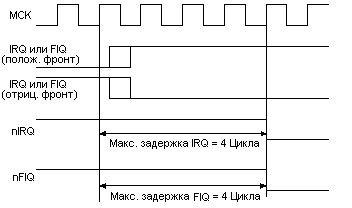

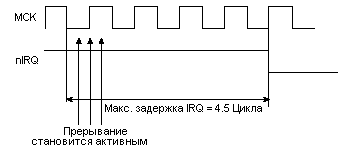

24.7.2.1 Источник внешнего прерывания по фронту

Рис. 24-6. Источник внешнего прерывания по фронту

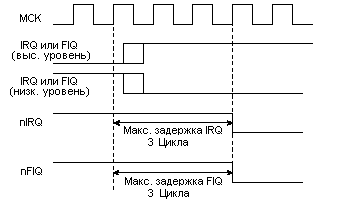

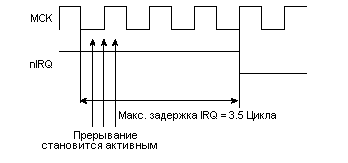

24.7.2.2 Источник внешнего прерывания по уровню

Рис. 24-7. Источник внешнего прерывания по уровню

24.7.2.3 Источник внутреннего прерывания по фронту

Рис. 24-8. Источник внутреннего прерывания по фронту

24.7.2.4 Источник внутреннего прерывания по уровню

Рис. 24-9. Источник внутреннего прерывания по уровню

24.7.3 Обычное прерывание

24.7.3.1 Контроллер приоритетов

Восьми уровневый контроллер приоритетов управляет сигналами nIRQ ядра, в зависимости от событий источников прерываний от 1 до 32 (кроме запрограммированных для быстрой обработки).

Каждому источнику прерывания можно задать уровень приоритета от 7 до 0, записью поля PRIOR соответствующего регистра режима источника AIC_SMR (Source Mode Register). Уровень 7 является наивысшим приоритетом.

В случае срабатывания прерывания по условию, определенному полем SRCTYPE регистра вектора прерываний AIC_SVR (Source Vector Register), устанавливается сигнал nIRQ. Так как может появиться новое прерывание от другого источника после появления сигнала nIRQ, контроллер прерываний определяет текущее прерывание в момент чтения регистра вектора прерываний AIC_IVR (Interrupt Vector Register). Чтение регистра AIC_IVR является точкой входа для программы обработки прерывания, которая позволяет контроллеру прерываний определить, какое прерывание стало обрабатываться программой.

Уровень текущего приоритета определяется уровнем текущего прерывания.

При срабатывании нескольких разрешенных источников прерывания одинакового приоритета после чтения регистра AIC_IVR в первую очередь обслуживается прерывание с наименьшим номером источника прерывания.

Сигнал nIRQ может быть сформирован только в случае срабатывания прерывания от источника с наивысшим приоритетом. Появляющееся новое прерывание (или прерывание в очереди) во время обработки текущего задерживается до момента, когда программа сообщит контроллеру прерываний об окончании обслуживания текущего прерывания записью в регистр окончания обработки прерывания AIC_EOICR (End of Interrupt Command Register). Запись в регистр AIC_EOICR - точка выхода из программы обработки прерывания.

24.7.3.2 Вложенность прерываний

Контроллер прерываний осуществляет вложение прерываний таким образом, чтобы прерывания более высокого приоритета обрабатывались во время обслуживания прерываний более низкого приоритета. Это требует от процедуры обработки прерывания более низкого приоритета возобновлять обработку прерывания на уровне ядра.

При появлении нового прерывания более высокого уровня во время обработки очередного сигнал nIRQ переподтверждается. Если прерывание разрешено на уровне ядра, текущее выполнение прерывается, и программа обслуживания нового прерывания должна прочитать регистр AIC_IVR. В это время номер текущего прерывания и его приоритет заносится во встроенный стек. Таким образом, происходит сохранение и восстановление информации по прерыванию после окончания обработки прерывания более высокого уровня и записи в регистр AIC_EOICR.

Контроллер прерываний оборудован 8-ми уровневым расширенным стеком для обслуживания до восьми вложенных прерываний, что требуется для организации восьми уровней приоритетов.

24.7.3.3 Векторы прерываний

Адрес программы обработки прерывания, соответствующий каждому источнику прерывания может храниться в регистрах векторов источников от AIC_SVR1 до AIC_SVR31 (Source Vector Registers). При чтении регистра вектора прерывания AIC_IVR (Interrupt Vector Register) возвращается значение, записанное в регистр AIC_SVR соответствующего текущего источника прерывания.

Данная особенность позволяет за одну команду обратиться к программе обработки текущего прерывания, так как регистр AIC_IVR расположен по абсолютному адресу 0xFFFF F100 и поэтому доступен из вектора прерываний ядра ARM по адресу 0x0000 0018, через следующую команду

LDR PC,[PC,# -&F20]

После исполнения команды, ядро загружает прочитанное значение из регистра AIC_IVR в программный счетчик. Таким образом, происходит переход на исполнение соответствующей программы обработки прерывания.

Данная особенность часто не используется, когда приложение основано на работе с операционной системой (как реального времени, так и нет). Операционные системы часто имеют одну точку входа для всех прерываний, и первая исполняемая задача определяет источник прерывания.

Однако при переносе операционной системы на контроллеры серии AT91 рекомендуется использовать векторы прерываний. Это можно осуществить, определив все регистры AIC_SVR всех источников прерываний, чтобы операционная система обрабатывала прерывания по адресам обработчиков прерываний. В этом случае применение векторов прерываний позволяет обслуживать прерывания особо критичные ко времени обработки специальным быстрым обработчиком, а не общим обработчиком прерываний операционной системы. Это облегчает поддержку задач обрабатываемых в реальном времени (входы/выходы видео/аудио буферов и программная обработка работы с периферийными модулями) для эффективной и независимой работы приложений, работающих в операционной системе.

24.7.3.4 Процедуры обработки прерываний

В этой части проводится обзор процедур обработки быстрых прерываний при использовании контроллера прерываний. Предполагается знание архитектуры ARM ядра, режимов прерываний и соответствующих статусных флагов.

Предположено, что:

- Контроллер прерываний запрограммирован, регистры AIC_SVR загружены адресами программ обработки прерываний и прерывания разрешены.

- Команда прерывания по адресу вектора прерывания должна работать с вектором прерываний

LDR PC, [PC, # -&F20]

При появлении сигнала nIRQ, и если флаг 'I' регистра CPSR сброшен, последовательность действий следующая:

- Регистр CPSR записывается в SPSR_irq, текущее значение программного счетчика загружается в регистр ссылки прерывания (R14_irq), а в программный счетчик (R15) загружается значение 0x18. В следующем цикле в течение выборки по адресу 0x1C, ядро ARM устанавливает R14_irq, уменьшая его значение на четыре.

- ARM ядро переходит в режим прерывания, если еще не находится в нем.

- После исполнения команды загруженной по адресу 0x18 программный счетчик загружается значением из регистра AIC_IVR. Чтение регистра AIC_IVR приводит к следующему:

- Текущее прерывание ставится в очередь на обработку, и разрешается прерывание более высокого приоритета. Текущий уровень приоритета соответствует уровню текущего прерывания.

- Сигнал nIRQ переопределяется. Даже если не используется вектор, регистр AIC_IVR должен быть прочитан для переопределения сигнала nIRQ.

- Автоматически сбрасывается прерывание, работающее по фронту.

- В стек заносится приоритет и номер текущего прерывания.

- Возвращается значение, записанное в регистр AIC_SVR соответствующего прерывания.

- Предыдущий шаг приводит к переходу к программе обработки прерывания. Это должно начинаться с сохранения регистра ссылки прерывания (R14_irq) и SPSR_IRQ. Регистр ссылки должен быть уменьшен на 4 после его сохранения, что требуется для его восстановления прямо в программный счетчик по окончании обработки прерывания. Например, может использоваться команда SUB PC, LR, #4.

- Далее прерывание демаскируется сбросом флага the "I" в регистре CPSR, позволяя ядру получать новый сигнал nIRQ. Это может произойти в случае появления прерывания более высокого приоритета.

- После этого продолжается обработка прерывания, сохраняются значения используемых регистров, восстанавливаемые по окончанию обработки. Появление прерывания более высокого уровня на этом этапе приведет к рестарту исполнительной последовательности с пункта 1.

Примечание. Если прерывание запрограммировано на срабатывание по уровню, то источник прерывания должен быть сброшен на этом этапе.

- Флаг "I" регистра CPSR должен быть установлен для маскирования прерываний перед выходом, чтобы убедиться в нормальном окончании обработки прерывания.

- Регистр окончания прерывания AIC_EOICR (End of Interrupt Command Register) должен быть записан, чтобы сообщить контроллеру прерываний о завершении обработки прерывания. Это приводит к обращению к стеку для восстановления информации по отложенному прерыванию, если такое было. Если поступает новое прерывание с более низким или таким же приоритетом как прерывание в стеке, но с более высоким приоритетом, чем текущее прерывание, сигнал nIRQ переназначается, но последовательность обработки прерывания автоматически не начинается, так как флаг "I" установлен в ядре. Регистр SPSR_irq восстанавливается. Далее сохраненное значение регистра ссылки восстанавливается в программный счетчик. Это приводит к возврату из прерывания в место продолжения программы, загрузке регистра CPSR значением из SPSR, маскированием или демаскированием прерываний в зависимости от состояния записанного в SPSR_irq.

Примечание. Установленный флаг "I" регистра SPSR информирует о том, что была прервана команда маскирования. Следовательно, после восстановления SPSR, команда маскирования завершается (прерывание маскировано).

24.7.4 Быстрое прерывание

24.7.4.1 Источник быстрого прерывания

Только 0-вой источник прерываний может вызвать быстрое прерывание, если не используется режим эмуляции быстрых прерываний (fast forcing). Нулевой источник прерывания обычно подключен к выводу FIQ микроконтроллера непосредственно или через контроллер PIO.

24.7.4.2 Управление быстрым прерыванием

Схема быстрых прерываний контроллера AIC не имеет контроллера приоритетов. Режимы 0-го источника прерывания задаются регистром AIC_SMRO. Поле PRIOR этого регистра не используется, даже если считывается то же значение, что было записано. Поле SRCTYPE регистра AIC_SMRO позволяет установить срабатывание быстрого прерывания, как по уровню, так и по фронту (положительному или отрицательному).

Запись 0x1 в регистр AIC_IECR (Interrupt Enable Command Register) и AIC_IDCR (Interrupt Disable Command Register) соответственно разрешает и запрещает быстрое прерывание. Нулевой бит регистра AIC_IMR (Interrupt Mask Register) информирует, разрешено или запрещено быстрое прерывание.

24.7.4.3 Векторы быстрых прерываний

Адрес процедуры обработки быстрого прерывания сохраняется в регистре AIC_SVR0 (Source Vector Register 0). Значение, записанное в этот регистр, возвращается после чтения регистра AIC_FVR (Fast Vector Register). Это позволяет обратиться к процедуре обработки прерывания через одну команду. Так как регистр AIC_FVR расположен по абсолютному адресу 0xFFFF F104 и поэтому доступен из вектора прерываний ядра ARM по адресу 0x0000 001С, через следующую команду

LDR PC,[PC,# -&F20]

После исполнения команды, ядро загружает прочитанное значение из регистра AIC_FVR в программный счетчик. Таким образом, происходит переход на исполнение соответствующей процедуры обработки быстрого прерывания. При этом автоматически сбрасывается источник быстрого прерывания, запрограммированный по фронту.

24.7.4.4 Процедуры обработки быстрого прерывания

В этой части проводится обзор процедур обработки быстрых прерываний при использовании контроллера прерываний. Предполагается знание архитектуры ARM ядра, режимов прерываний и соответствующих статусных флагов.

Предположено, что:

- Контроллер прерываний запрограммирован, регистр AIC_SVR0 загружен адресом процедуры обработки быстрого прерывания и 0-ой источник прерывания разрешен.

- Команда по адресу 0x1C (адрес вектора быстрого прерывания) для обращения к вектору быстрого прерывания

LDR PC, [PC, # -&F20]

- Пользователю не требуются вложенные быстрые прерывания

При появлении сигнала nFIQ, и если флаг 'F' регистра CPSR сброшен, последовательность действий следующая:

- Регистр CPSR записывается в SPSR_fiq, текущее значение программного счетчика загружается в регистр ссылки прерывания FIQ (R14_FIQ), а в программный счетчик (R15) загружается значение 0x1C. В следующем цикле в течение выборки по адресу 0x20, ядро ARM устанавливает R14_fiq, уменьшая его значение на четыре.

- ARM ядро переходит в режим быстрого прерывания FIQ.

- После исполнения команды загруженной по адресу 0x1С программный счетчик загружается значением из регистра AIC_FVR. Чтение регистра AIC_FVR приводит к автоматическому сбросу быстрого прерывания, срабатывающего по фронту. Только в этом случае происходит сброс сигнала nFIQ.

- Предыдущий шаг приводит к переходу к процедуре обработки прерывания. Сохранять регистр ссылки прерывания (R14_fiq) и SPSR_FIQ не требуется, так как отсутствует вложение быстрых прерываний.

- После этого продолжается обработка прерывания. Сохранять регистры R8 R13 не требуется, так как для режима FIQ отведены собственные регистры. Остальные регистры, R0 R7, должны быть сохранены перед их использованием, а затем восстановлены. Заметим, что если быстрое прерывание запрограммировано на срабатывание по уровню, то источник прерывания должен быть сброшен на этом этапе, для разрешения последующего прерывания 0-го источника.

- Наконец, регистр ссылки R14_FIQ сохраняется в программный счетчик PC после уменьшения его на 4. Например, можно применить команду SUB PC, LR, #4. Это приводит к возврату из прерывания в место продолжения программы, загрузке регистра CPSR значением из SPSR, маскированием или демаскированием прерываний в зависимости от состояния записанного в SPSR.

Примечание. Установленный флаг "F" регистра SPSR сообщает, что была прервана команда маскирования быстрого прерывания. Следовательно, после восстановления SPSR, маскирование прерванной команды завершается (быстрое прерывание замаскировано).

Другой способ обработать быстрое прерывание - разместить процедуру обработки прерывания по адресу вектора ARM ядра 0x1C. В этом случае векторы не используются, при этом чтение AIC_FVR должно быть выполнено в самом начале процедуры обработки прерывания. Однако, при этом методе остается возможность исполнения расширенных инструкций.

24.7.4.5 Режим эмуляции быстрого прерывания (Fast Forcing)

В режиме эмуляции быстрого прерывания контроллер прерываний перенаправляет любой обычный источник прерывания на контроллер быстрого прерывания.

Разрешение или запрет этого режима осуществляется записью в регистр разрешения эмуляции быстрого прерывания AIC_FFER (Fast Forcing Enable Register) и в регистр запрета эмуляции быстрого прерывания AIC_FFDR (Fast Forcing Disable Register). В результате записи этих регистров обновляется регистр статуса эмуляции быстрого прерывания AIC_FFSR (Fast Forcing Status Register), контролирующий режимы любого источника прерывания, как внутреннего, так и внешнего.

При запрещенном режиме эмуляции быстрого прерывания источники прерываний обрабатываются, как было описано выше.

В режиме эмуляции быстрого прерывания, в некоторых случаях определение прерываний, запрограммированных по фронту, не приводит к срабатыванию нормального прерывания, и может не обработаться обработчиком приоритетов.

Запрограммированный источник прерывания по уровню при срабатывании по уровню в режиме быстрого прерывания приводит к срабатыванию сигнала nFIQ для ядра.

Запрограммированный источник прерывания по фронту при срабатывании по фронту в режиме быстрого прерывания приводит к срабатыванию сигнала nFIQ для ядра.

Режим эмуляции быстрого прерывания не влияет на бит 0-го источника в регистре AIC_IPR (Interrupt Pending Register).

Регистр векторов быстрого прерывания AIC_FVR (Fast Interrupt Vector Register) считывает содержимое 0-го регистра вектора прерываний AIC_SVR0 (Source Vector Register 0), независимо от того, какой был источник быстрого прерывания. Чтение регистра FVR не сбрасывает 0-ой источник прерывания при использовании режима эмуляции быстрого прерывания и сброс источника прерывания производится записью в регистр сброса прерывания AIC_ICCR (Interrupt Clear Command Register).

Все разрешенные и обрабатываемые источники прерываний с разрешенным режимом эмуляции быстрого прерывания, и запрограммированные на срабатывание по фронту должны очищаться записью в регистр сброса прерывания. В этом случае прерывания очищаются независимо, что предотвращает потерю прерываний.

Чтение регистра AIC_IVR не сбрасывает источник прерывания, для которого был включен режим эмуляции быстрого прерывания.

Нулевой источник прерывания, предназначенный для быстрого прерывания, продолжает работать нормально и становится одним из источников быстрых прерываний.

Рис. 24-10. Быстрые прерывания

24.7.5 Защищенный режим

В защищенном режиме чтение регистра вектора прерываний возможно без выполнения связанных с этим автоматических операций. Это может понадобиться в режиме отладки. Когда отладчик, работающий как с модулем ICE ARM ядра, так и с Debug Monitor, останавливает приложение и обновляет открытые окна, он может прочитать данные по контроллеру прерывания и соответственно регистр IVR. Это может привести к нежелательным последствиям:

- поступающее разрешенное прерывание с более высоким приоритетом, чем текущее в очереди, заносится в стек

- если больше нет разрешенных прерываний в очереди, возвращается случайный вектор.

В любом случае, необходимо подтверждать команду окончания прерывания и восстанавливать контекст контроллера прерываний. Эта операция не представлена в отладочных системах, так как в этом случае отладочная система становится "тяжелой" и может перевести приложение в неизвестное состояние.

Это предотвращается применением защищенного режима. Запись DBGM в регистр управления отладки AIC_DCR (Debug Control Register) 0x1 включает защищенный режим.

В защищенном режиме контроллер прерываний выполняет запись в стек по прерываниям только в случае осуществления записи в регистр AIC_IVR. Поэтому, процедура обработки прерывания должна записывать (произвольные данные) в регистр AIC_IVR только после его чтения. Новый контекст контроллера прерываний, включая значение регистра статуса прерываний AIC_ISR (Interrupt Status Register), обновляется текущим прерыванием только после записи регистра AIC_IVR.

Прочитанное собственное значение AIC_IVR, например отладчиком, не изменяет ни контекст контроллера прерываний, ни значение регистра AIC_IVR. Чтение расширенного AIC_IVR приводит к таким же операциям. Однако, рекомендуется не останавливать ядро между чтением и записью регистра AIC_IVR в процедуре обработки прерывания, чтобы убедиться в том, что отладчик не изменит контекст контроллера прерываний.

В заключение, в нормальном режиме работы, чтение AIC_IVR осуществляет следующие операции с контроллером прерываний:

- Вычисление активного прерывания (более высокого, чем текущее или случайное)

- Определение и возврат вектора активного прерывания

- Запоминание прерывания

- Занесение приоритета текущего прерывания во внутренний стек

- Подтверждение приема прерывания

Однако, в защищенном режиме выполняются только пункты с 1-го по 3-ий при чтении регистра AIC_IVR. Пункты 4 и 5 выполняются контроллером прерываний только при записи в AIC_IVR.

Программы, написанные и отлаженные с использованием защищенного режима, правильно работают и в обычном режиме без изменений в коде. Однако, в обычном режиме запись в регистр AIC_IVR не требуется и может быть удалена, чтобы оптимизировать код.

24.7.6 Случайное прерывание

Контроллер прерываний имеет защиту против случайных прерываний. Случайное прерывание определяется как появление сигнала от источника прерывания достаточного по времени для вырабатывания контроллером прерывания сигнала nIRQ, но уже отсутствующего при чтении регистра AIC_IVR. Чаще всего это происходит когда:

- Внешний источник прерывания запрограммирован на срабатывание по уровню, а активный уровень появляется только на короткое время.

- Внутренний источник прерывания запрограммирован на срабатывание по уровню, а выходной сигнал соответствующего внешнего периферийного модуля активизируется только на короткое время (как например в случае с Watchdog-ом).

- Прерывание появляется только на время нескольких тактов, перед тем как программа произведет его маскирование, что приведет к появлению импульса от источника прерывания.

Контроллер прерываний определяет появление случайных прерываний во время чтения регистра AIC_IVR, пока не рассматривается ни один из разрешенных источников прерываний. Если это случается, контроллер прерываний возвращает значение предварительно сохраненное в регистре вектора случайного прерывания AIC_SPU (Spurious Vector Register). Программа должна хранить адрес процедуры обработки случайного прерывания в AIC_SPU, для обеспечения возврата к нормальному выполнению программы как можно скорее. Эта процедура записывает в регистр AIC_IEOICR и осуществляет возврат из прерывания.

24.7.7 Маскирование общих прерываний

Особенность контроллера прерываний - маскирование общих прерываний, чтобы предотвратить их подачу на процессор. Сигналы nIRQ и nFIQ переводятся в неактивное состояние, если бит GMSK в регистре управления отладки AIC_IDCR (Debug Control Register) установлен. Однако данная маска не предотвращает пробуждение процессора, если он находился в холостом режиме. Эта функция облегчает синхронизацию ядра по последующему событию, как только это событие совершается, выполняется последовательность операций не требующая выполнения прерывания. Эту маску рекомендуется использовать с большой осторожностью.

|