19.3 Функциональное описание

Контроллер памяти руководит работой шины ASB и осуществляет обработку и выполнение запросов от обоих ведущих модулей: процессор ARM7TDMI и контроллер ПДП периферийных модулей.

Контроллер памяти состоит из следующих узлов:

- арбитр шины,

- дешифратор адреса,

- контроллер исключительных ситуаций при работе с памятью,

- детектор ошибок выравнивания,

- контроллер встроенной флэш-памяти.

Контроллер памяти может выполнять работу только в режиме little-endian (более младшие байты слов размещаются по младшим адресам памяти). Оба ведущих модуля (см. выше) также функционируют только в режиме little-endian.

19.3.1 Арбитр шины

Контроллер памяти имеет в своем составе простой арбитр шины (bus arbiter), который единовременно предоставляет управление шиной только одному из ведущих модулей: процессору ARM7TDMI и контроллеру ПДП периферийных модулей, имеющие жестко заданные приоритеты при доступе к шине: контроллер ПДП имеет наивысший приоритет, а процессор - низший приоритет.

19.3.2 Дешифратор шины адреса

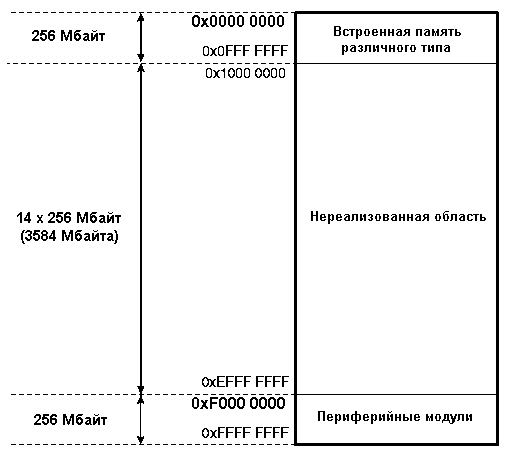

Одной из особенностей контроллера памяти является наличие в его составе дешифратора адреса (address decoder), который с помощью четырех самых старших бит 32-битного адреса разделяет все адресное пространство на три непересекающихся области:

- область размером 256 Мбайт - адресное пространство для внутренней памяти,

- область размером 256 Мбайт - адресное пространство для периферийных модулей,

- область размером 3584 Мбайта, состоящая из 14-ти областей по 256 Мбайт каждая, попытки обращения к которым вызывают аварийную исключительную ситуацию (Abort).

Рисунок 19-2. Карта распределения памяти при работе дешифратора адреса

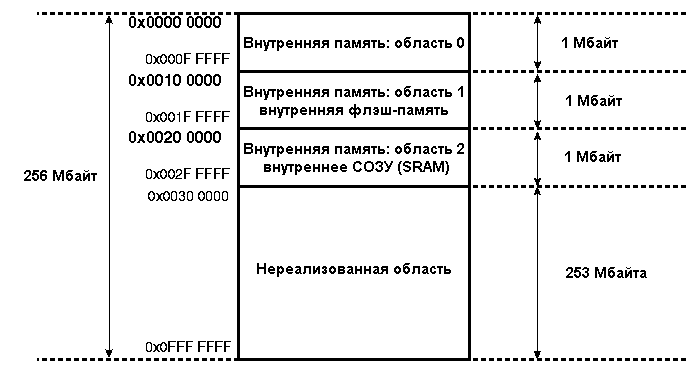

19.3.2.1 Карта распределения внутренней памяти

В пределах всего 256-Мбайтного адресного пространства внутренней памяти дешифратор адреса контроллера памяти адресует 256 областей, каждая размером 1 Мбайт (за выбор области отвечают восемь соответствующих бит из 32-битного адреса).

Все адресное пространство внутренней памяти разделено на равные участки памяти - области размером 1 Мбайт каждая. Для каждого из видов памяти отводится одна такая целая область (см. рис. 19-3). Вся распределенная внутренняя память размещена в диапазоне адресов 0x0000 0000…0x002F FFFF.

Попытки доступа к нераспределенным областям внутренней памяти (0x0030 0000…0x0FFF FFFF) вызывают аварийную исключительную ситуацию (Abort).

Рисунок 19-3. Карта распределения внутренней памяти

19.3.2.2 Начальная область внутренней памяти (область 0)

Первые 32 байта начальной области внутренней памяти (область 0) содержит векторы обработчиков исключительных ситуаций и прерываний, в частности, вектор сброса размещен по нулевому адресу 0x0000 0000.

Перед выполнением команды перераспределения памяти (remap) на начальную область (область 0) отображена встроенная флэш-память (область 1), поэтому при старте процессора выполнение программы будет всегда производиться из встроенной флэш-памяти. После выполнения команды перераспределения памяти на начальную область отображается встроенная статическая память СОЗУ (область 2). В этом случае доступ к СОЗУ возможен как через область 0, так и через область 2 (см. рис. 19-3), при этом обращение производится физически к одной и той же памяти.

19.3.3 Команда перераспределения памяти

После окончания выполнения команды перераспределения памяти (remap), внутренняя встроенная статическая память СОЗУ становиться также доступной через область 0 внутренней памяти.

Все векторы ядра ARM: сброс, авария, авария данных, авария при выборке, неопределенная команда, прерывание и быстрое прерывание (Reset, Abort, Data Abort, Prefetch Abort, Undefined Instruction, Interrupt, Fast Interrupt) размещены в области памяти по адресам 0x0000 0000…0x0000 0020. После выполнения команды перераспределения памяти появляется возможность динамического переопределения этих векторов в процессе работы программы.

Доступ к выполнению команды перераспределения памяти осуществляется через пользовательский интерфейс контролера памяти. Для выполнения этой команды необходимо установить флаг RCB в регистре MC_RCR.

Сброс флага RCB в регистре MC_RCR вызывает отмену команды перераспределения памяти. Это упрощает процесс отладки последовательности загрузки, определяемой пользователем, предоставляя простой способ перезапуска процессора без необходимости его сброса.

19.3.4 Аварийная исключительная ситуация (Abort)

Существуют две причины вызова исключительной ситуации:

- доступ к нереализованной области памяти,

- доступ к памяти по не выровненному по границе слова (полуслова) адресу.

При возникновении исключительной ситуации (вне зависимости от её источника) сигнал Abort передается всем ведущим модулям: процессор ARM7TDMI и контроллер ПДП периферийных модулей. Однако только ядро процессора ARM7TDMI принимает во внимание этот сигнал, и только при условии того, что была осуществлена попытка доступа к памяти. Сигнал Abort не влияет на контроллер ПДП периферийных модулей (сигнал Abort даже не подключен к контроллеру ПДП - см. рис. 19-1).

В контроллер памяти встроен регистр статуса аварийной ситуации (Abort Status Register). Что упрощает процесс отладки приложения и позволяет встраиваемой операционной системе проводить анализ причины возникновения аварийной ситуации. Адрес ячейки памяти, доступ к которой вызвал аварийную исключительную ситуацию, сохраняется в регистре MC_AASR, а параметры доступа - в регистре MC_ASR и включают следующее:

- размер запроса (поле ABTSZ);

- тип доступа: чтение, запись или выборка кода команды (поле ABTTYP);

- доступ к нереализованной области памяти (флаг UNDADD) или попытка выполнения неопределенной команды (флаг MISADD);

- источник попытки доступа при последнем возникновении аварийной ситуации (флаги MST0 и MST1);

- было ли зафиксировано повторное возникновение аварийной ситуации с момента последнего чтения регистра MC_ASR (флаги SVMST0 и SVMST1).

В том случае, если источником аварийной ситуации является процессор (Data Abort), то сохраняется этот "аварийный" адрес памяти. Это особенно полезно для поиска причины аварийной ситуации: изучение кода команды, размещенной по этому адресу, и текущее содержимое регистров процессора позволяют полностью изучить причину проблемы и принять решение о дальнейших действиях.

В том случае, если возникла аварийная ситуация при выборке кода команды (Prefetch Abort), то адрес этой команды уже не удастся определить, поскольку сама команда уже размещена в буфере предвыборки ARM процессора. Поэтому процессор ARM принимает во внимание аварийную ситуацию Prefetch Abort только тогда, когда уже происходит непосредственно выполнение самой этой команды. Более того, существует вероятность того, что между выборкой сбойной команды и ее выполнением были повторно зафиксирована одна или более аварийных ситуаций. Таким образом, для анализа таких аварийных ситуаций рекомендуется использовать содержимое регистра ссылки (Link Register - LR) процессора.

19.3.5 Контроллер встроенной флэш-памяти

Контроллер встроенной флэш-памяти (EFC) является частью контроллера памяти (MC) и предоставляет интерфейс для доступа к блокам флэш-памяти по внутренней 32-битной шине. Это позволяет значительно увеличить скорость выборки команд из флэш-памяти при работе ядра процессора в режиме Thumb (16-битная система команд) благодаря работе 32-битного буфера. Более того, контроллер встроенной флэш-памяти поддерживает выполнение полного набора команд для чтения, записи, стирания флэш-памяти, установки и снятия битов защиты.

19.3.6 Детектор ошибок выравнивания

Встроенный в контроллер памяти детектор ошибок выравнивания контролирует корректность обращения к памяти.

При каждом обращении к памяти (вне зависимости от её источника) детектор ошибок выравнивания производит проверку типа размерности данных и младших двух бит адреса памяти, по которому производится это обращение. Если тип размерности данных - слово (32 бита) и младшие два бита адреса - не нулевые, или типа размерности данных - полуслово (16 бит) и младший бит адреса - не нулевой, то формируется сигнал аварии и обращение к памяти отменяется. Однако, такая проверка не производится при выборке команды процессором ARM.

Как правило, ошибки выравнивания возникают в процессе создания программы (так называемые программные "баги") и чаще всего связаны с некорректной работой с указателями. При отладке программы подобные ошибки зачастую бывает очень трудно обнаружить.

Адрес ячейки памяти, обращение к которой вызвало ошибку выравнивания, сохраняется в регистре статуса аварийной ситуации (Abort Status Register), а адрес команды, выполнение которой вызвало эту ошибку, сохраняется в регистре ссылки аварийной ситуации (Abort Link Register) процессора ARM. Поэтому определение этой программной ошибки и ее устранение значительно упрощаются.

|