14.3 Функциональное описание

Контроллер сброса построен на базе контроллера вывода NRST (NRST Manager), контроллера супервизора питания (Brownout Manager), стартового счетчика (Startup Counter) и контроллера состояний сброса (Reset State Manager). Все эти узлы тактируются от низкочастотного тактового сигнала (Slow Clock) и формируют следующие сигналы сброса:

- proc_nreset: сигнал сброса для процессора и сторожевого таймера

- periph_nreset: сигнал сброса для всех встроенных периферийных узлов

- nrst_out: непосредственное управление выводом NRST

Все эти сигналы сброса формируются контроллером сброса, который управляется по внешним либо программным событиям либо. Контроллер состояний сброса управляет формированием сигналов сброса и сигнала для контроллера вывода NRST.

Контроллер вывода NRST позволяет управлять длительностью выходного сигнала сброса на этом выводе, который может быть подключен к выводам сброса внешних компонентов.

14.3.1 Контроллер вывода NRST

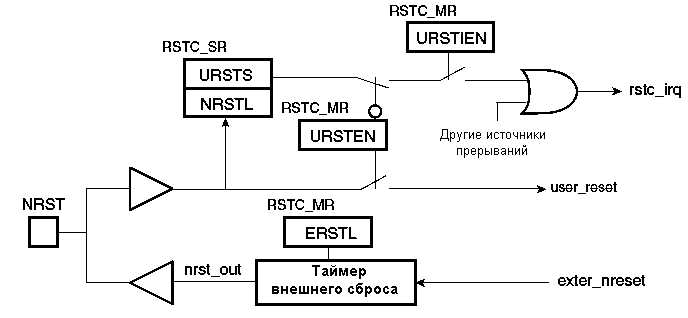

Контроллер вывода NRST предназначен для контроля над состоянием входа NRST (с некоторой заданной периодичностью) и управления выходным буфером этого вывода по требованию контроллера состояний сброса. На рис. 14-2 изображена структурная схема контроллера вывода NRST.

Рисунок 14-2. Структурная схема контроллера вывода NRST

14.3.1.1 Сигнал NRST или прерывание

Контроллер вывода NRST проверяет состояние на входе NRST через равные промежутки времени, зависящие только от частоты низкочастотного тактового сигнала (Slow Clock). При обнаружении на выводе NRTS низкого логического уровня формируется сигнал "внешний сброс" (User Reset), который поступает на вход контроллера состояний сброса (Reset State Manager).

В то же время, контроллер вывода NRST может быть запрограммирован так, что не будет реагировать на смену состояния на выводе NRST. Сброс флага URSTEN в регистре RSTC_MC запретит внешний аппаратный сброс (User Reset).

В любой момент времени можно программно определить текущей логический уровень на входе NRST с помощью флага NRSTL (NRST Level), размещенного в регистре RSTC_SR. Как только будет зафиксирован низкий логический уровень на входе NRST, будет установлен флаг URSTS в регистре RSTC_SR. Сброс этого флага возможен только по чтению регистра RSTC_SR.

Контроллер вывода NRST может быть запрограммирован для формирования сигнала прерывания по сбросу. Для этого необходимо установить флаг URSTIEN в регистре RSTC_MR.

14.3.1.2 Формирование внешнего сигнала сброса

Контроллер состояний сброса (Reset State Manager) формирует сигнал ext_nreset для формирования сигнала внешнего сброса на выводе NRST. В этом случае сигнал nrst_out, управляющий непосредственно выходным буфером NRST, принимает низкий логический уровень (через контроллер вывода NRST) на определенное время, задаваемое в поле ERSTL регистра RSTC_MR.

Длительность этого сигнала (EXTERNAL_RESET_LENGTH) вычисляется по формуле: 2(ERSTL+1) импульсов низкочастотного тактового сигнала (Slow Clock). Таким образом, длительность сигнала nrst_out программируется в диапазоне от 60 мкс до 2 сек. Если ERSTL=2, то длительность импульса внешнего сброса на выводе NRST будет равна двум периодам низкочастотного тактового сигнала.

Эта особенность позволяет контроллеру сброса фактически увеличивать длительность сигнала сброса на столько на, сколько этого требуется для стабильного сброса внешних компонентов схемы.

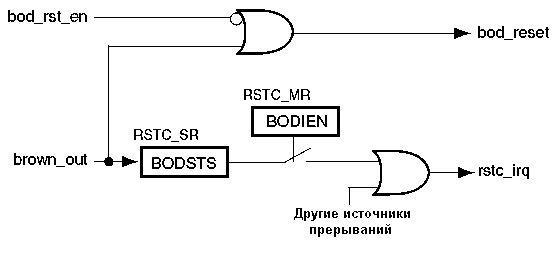

14.3.2 Контроллер супервизора питания

Контроль над провалом напряжения питания (супервизор питания) позволяет предотвращать переход процессора в непредсказуемые состояния, если питание процессора падает ниже заданного уровня. Когда напряжение VDDCORE падает ниже определенного порога срабатывания внутреннего компаратора супервизор питания, то контроллер супервизор питания (Brownout Manager) формирует сигнал сброса bod_reset.

С помощью внешнего программатора возможно отключение сброса от супервизора питания посредством перевода сигнала bod_rst_en в низкий логический уровень, т.е. блокировкой соответствующего NVM бита общего назначения в флэш-памяти. В этом случае провалы напряжения VDDCORE не будут вызывать сброс микроконтроллера. Также факт срабатывания внутреннего компаратора супервизора питания можно проконтролировать через флаг BODSTS регистра RTSC_SR. Сброс этого флага возможен только по чтению регистра RSTC_SR.

При установленных флагах BODSTS (регистр RTSC_SR) и BODIEN (регистр RSTC_MR) разрешено формирование сигнала прерывания от супервизора питания.

По-умолчанию при изготовлении микроконтроллера сброс от супервизора питания запрещен.

Рисунок 14-3. Контроллер супервизора питания

14.3.3 Состояния сброса

Контроллер состояний сброса (Reset State Manager - RSM) управляет различными источниками сброса и формирует соответствующие внутренние сигналы сброса. Текущее состояние сброса определено в поле RSTTYP регистра статуса RSTC_SR. Обновление содержимого этого поля будет происходить только тогда, когда сигнал сброса процессора отпущен.

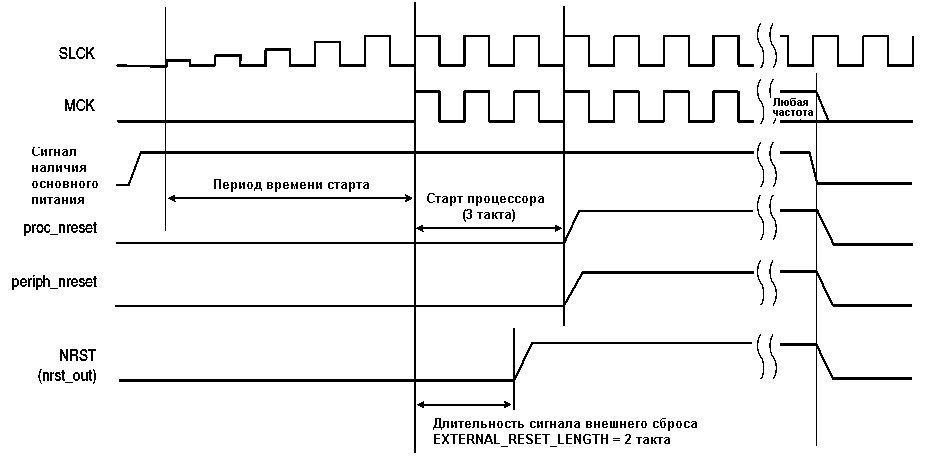

14.3.3.1 Сброс при подаче питания (Power-up Reset)

При подаче питания на выводы VDDCORE узел по контролю над питанием формирует задержку на некоторое время, необходимое для надежной стабилизации частоты низкочастотного тактового сигнала (Slow Clock) до того.

Временя запуска (см. рис. 14-4) микроконтроллера жестко связано со временем запуска генератора низкочастотного тактового сигнала. После завершения этого промежутка времени освобождается сигнал сброса, после чего в поле RSTTYP регистра RSTC_SR будет указана причина этого сброса: сброс при подаче питания.

Как только будет зафиксировано падение напряжения VDDCORE, то немедленно возникнут все сигналы сброса.

Рисунок 14-4. Сброс при подаче питания

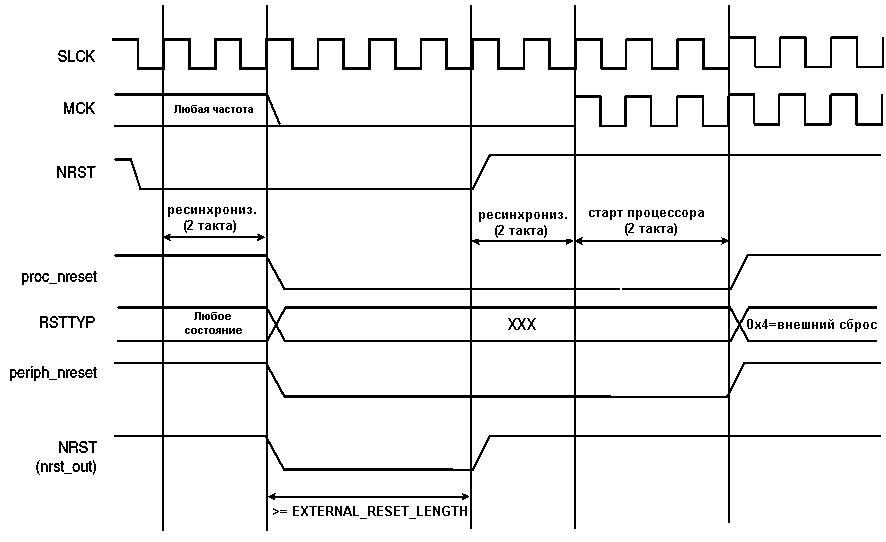

14.3.3.2 Внешний сброс

Внешний сброс (User Reset) возникает только тогда, когда на входе NRST будет зафиксирован низкий логический уровень и будет установлен флаг URSTEN регистра RSTC_MR. Логическое состояние на входе NRST стробируется тактовым сигналом SCLK для обеспечения правильной работы системы.

Внешнего сброса вызывает немедленное формирование сигналов сброс ядра процессора и периферийных модулей микроконтроллера.

Как только на входе NRST будет зафиксирован высокий логический уровень (после возникновения внешнего сброса), то сразу после этого будет сформирована задержка на два такта SCLK для ресинхронизации три такта MCK для формирования задержки запуска процессора. Тактирование процессора (MCK) будет приостановлено на время удержания входа NRST в низком логическом состоянии.

После завершения сброса в поле RTSTYP регистра статуса RSTC_SR будет записано значение 0x4, свидетельствующее о том, что был выполнен внешний аппаратный сброс (User Reset).

Контроллер вывода NRST гарантирует, что низкий логический уровень будет присутствовать на выводе NRST как минимум время EXTERNAL_RESET_LENGTH, определяемое в поле ERSTL числом периодов низкочастотного тактового сигнала (Slow Clock). Однако, если на входе NRST принудительно внешне присутствует низкий уровень дольше, чем указанное выше время, то микроконтроллер будет находиться в состоянии сброса до тех пор, пока на выводе вновь не возникнет высокий логический уровень.

Рисунок 14-5. Внешний сброс

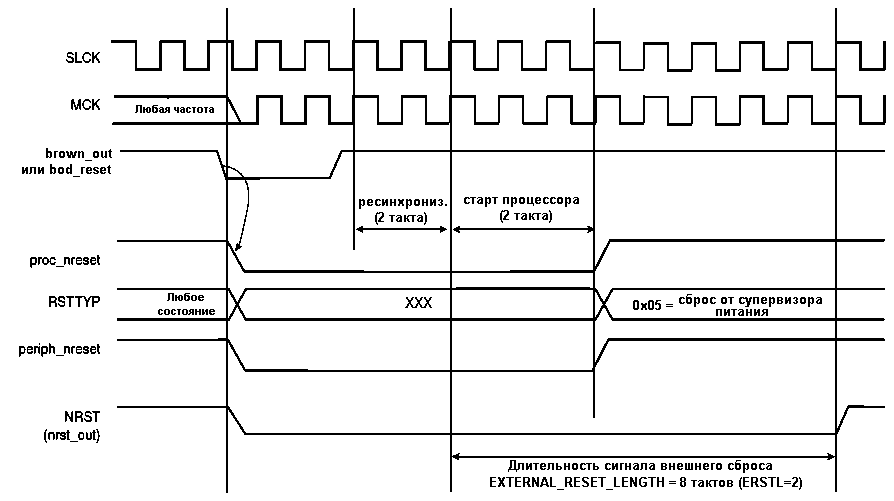

14.3.3.3 Сброс при провалах напряжения питания

Когда возникают сигнал brown_out/bod_reset (активный уровень - низкий), то контроллер состояний сброса немедленно формирует сброс от супервизора питания (Brownout Reset). В этом случае в состоянии сброса будут находиться ядро процессора, встроенные периферийные модули и вывод внешнего сброса NRST.

Как только на напряжение питания вновь возрастет до необходимого уровня (по фронту сигнала brown_out/bod_reset), то сразу после этого будет сформирована задержка на два такта SCLK (ресинхронизация на три такта MCK) для формирования задержки запуска процессора. В течение всего этого времени тактирование процессора (сигнал MCK) не приостанавливается.

Как только процессор выйдет из состояния сброса, в поле RSTTYP регистра RSTC_SR будет записано значение 0x5, указывающее на то, что произошел сброс по причине провала напряжения питания VDDCORE.

Рисунок 14-6. Сброс при провалах напряжения питания

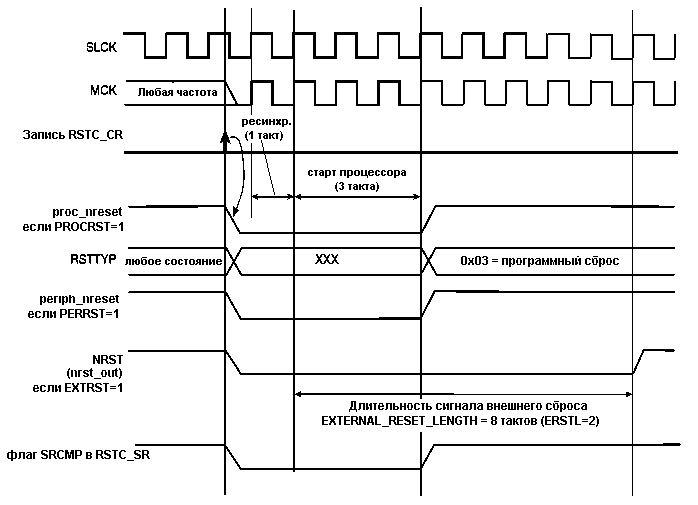

14.3.3.4 Программный сброс

Контроллер сброса имеет несколько команд, выполнение которых позволяет сформировать различные сигналы сброса. Выполнение этих команд происходит при установке следующих флагов регистра управления (RSTC_CR).

- PROCRST: сброс ядра процессора и сторожевого таймера

- PERRST: сброс встроенных периферийных модулей, включая систему памяти, и в частности команду перераспределения памяти (Remap). Обычно сброс периферийных модулей используется при отладке.

- EXTRST: формирование сигнала сброса на выводе NRST в течение промежутка времени, задаваемого в поле ERSTL регистра режима (RSTC_MR).

Программный сброс возникает, если программно установлен хотя бы один из указанных выше флагов. Все эти команды выполняются независимо друг от друга, поэтому могут быть вызваны поочередно или одновременно. Программный сброс длится 3 периода низкочастотного тактового сигнала (Slow Clock).

Установка внутренних сигналов сброса привязана к тактовому сигналу MCK, а их освобождение - к сигналу SCK.

Если установлен флаг EXTRST, то формируется сигнал nrst_out с программно управляемой длительностью (поле ERSTL). Однако при этом переход состояния входа NRST из высокого в низкий логический уровень не будет вызывать внешний аппаратный сброс (User Reset).

Только установка флага PROCRST будет вызывать фиксацию в поле RSTTYP регистра статуса (RSTC_SR) причины сброса - программный сброс. Формирование остальных видов программного сброса не будет зафиксирована в поле RSTTYP.

Как только возникает программный сброс, то сразу устанавливается флаг "выполнение команды программного сброса" SRCMP (Software Reset Command in Progress) в регистре статуса (RSTC_SR). При этом пока этот флаг установлен, то игнорируются попытки выполнения других команд программного сброса: игнорируется запись любых значений в регистр RSTC_CR. Как программный сброс завершиться, то флаг SRCMP автоматически аппаратно будет сброшен.

Рисунок 14-7. Программный сброс

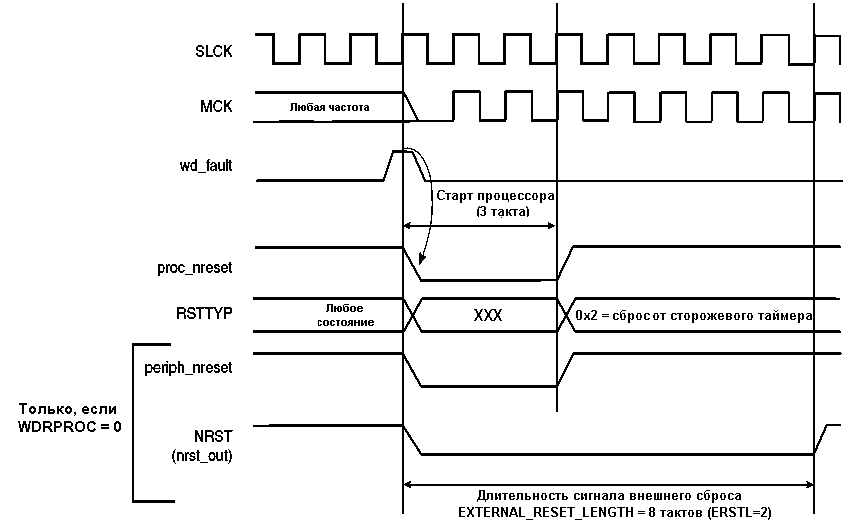

14.3.3.5 Сброс от сторожевого таймера

Сброс от сторожевого таймера (Watchdog Reset) возникает при срабатывании сторожевого таймера. В этом случае сброс длится три периода низкочастотного тактового сигнала (Slow Clock).

При возникновении сброс от сторожевого таймера возможны следующие ситуации, зависящие от состояния флага WDTPROC в регистре WDT_MR.

- WDTPROC = "0": возникает сброс ядра процессора и периферийных модулей, в том числе и внешний сброс NRST (длительность сброса зависит от содержимого поля ERSTL). Однако, переход состояния входа NRST из высокого в низкий логический уровень не будет вызывать внешний аппаратный сброс (User Reset).

- WDTPROC = "1": возникает сброс только ядра процессора.

Сброс самого сторожевого таймера вызывается сигналом proc_nreset. Так как срабатывание сторожевого таймера всегда вызывает сброс ядра процессора, то при установленном флаге WDRSTEN будет происходить сброс самого сторожевого таймера при возникновении от него сброса. После сброса сторожевой таймер всегда включен, а период его срабатывания устанавливается на максимальное значение.

Если флаг WDRSTEN в регистре WDT_MR сброшен, то срабатывание сторожевого таймера не вызывает сброс микроконтроллера.

Рисунок 14-8. Сброс от сторожевого таймера

14.3.4 Приоритеты источников сброса

Приоритеты различных источников сброса определяет контроллер состояний сброса (Reset State Manager) в указанном ниже порядке.

- Сброс при подаче питания

- Сброс при провалах напряжения питания

- Сброс от сторожевого таймера

- Программный сброс

- Внешний аппаратный сброс

Ниже указаны частные случаи сброса.

- В состоянии внешнего аппаратного сброса.

- События от сторожевого таймера не могут возникать по причине того, что сам сторожевой таймер находится в состоянии сброса из-за наличия сигнала proc_nreset.

- Программный сброс так же невозможен по той же причине.

- В состоянии программного сброса.

- Сброс от сторожевого таймера игнорируется, так как имеет меньший приоритет по сравнению с приоритетом программного сброса.

- Изменения состояния на входе NRST игнорируется.

- В состоянии от сторожевого таймера.

- Поскольку процессор в этом случае находится в состоянии сброса, то программный сброс уже невозможен.

- Внешний аппаратный сброс игнорируется, так как имеет меньший приоритет по сравнению с приоритетом сброса от сторожевого таймера

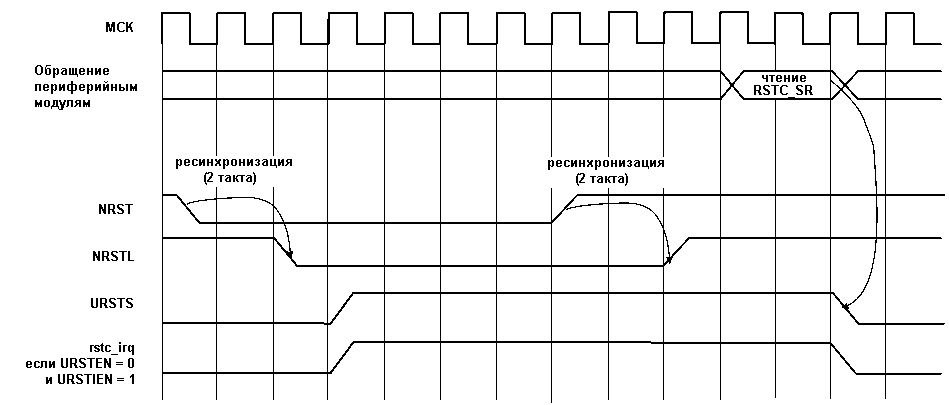

14.3.5 Регистр статуса контроллера сброса

Регистр статуса контроллера сброса (RSTC_SR) содержит несколько описанных ниже полей.

- Поле RSTTYP: позволяет определить источник последнего произошедшего сброса.

- Флаг SRCMP: информирует о том, что в данный момент выполняется команда программного сброса. В это время все попытки выполнения других видов программного сброса игнорируются. После завершения программного сброса этот флаг будет автоматически аппаратно сброшен.

- Флаг NRSTL: содержимое этого флага соответствует текущему состоянию на входе NRST, стробируемого по каждому переднему фронту сигнала MCK.

- Флаг URSTS: переключение логического уровня на входе NRST из высокого в низкое вызывает установку флага URSTS в регистре RSTC_SR. Это событие привязано к переднему фронту сигнала MCK (см. рис. 14-9). Если запрещен внешний сброс (URSTEN = 0), но при этом разрешено прерывание (установлен флаг URSTIEN в регистре RSTC_MR), то возникнет соответствующее прерывание. Чтение статусного регистра RSTC_SR вызывает сброс флага URSTS и самого сигнала этого прерывания (rstc_irq).

- Флаг BODSTS: информирует о том, что возник сигнал сброса от супервизора питания (зафиксирован провал напряжения питания VDDCORE), если сам сброс запрещен (bod_rst_en = 0). При этом будет вызвано соответствующее прерывание, если оно разрешено: установлен флаг BODIEN в регистре разрешения прерываний RTSC_MR. Чтение статусного регистра RSTC_SR вызывает сброс флага BODSTS и самого сигнала этого прерывания (bod_irq).

Рисунок 14-9. Статус контроллера сброса и сигналы прерываний от него

|